Przeszukaj forum

Pokazywanie wyników dla tagów 'CMOS camera'.

Znaleziono 2 wyniki

-

CMOS Camera Sensor(OV7670) - filtr wykrywanie krawędzi.

FlyingDutch opublikował temat w Układy programowalne

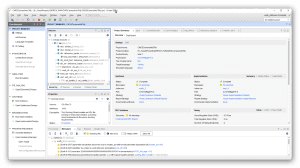

Cześć, po pierwszej próbie podłączenia prostego sensora kamery VGA (OV7670) do zestawu FPGA postanowiłem spróbować czegoś trochę bardziej skomplikowanego - wykrywania krawędzi obrazu z kamery. Jeśli kogoś interesują podstawowe informacje dot. teorii działania jednego z najczęściej używanych filtrów do detekcji krawędzi w obrazie "Filtru Sobl'a", to tutaj podaję linki: https://en.wikipedia.org/wiki/Sobel_operator https://medium.com/datadriveninvestor/understanding-edge-detection-sobel-operator-2aada303b900 https://homepages.inf.ed.ac.uk/rbf/HIPR2/sobel.htm Do implementacji wybrałem projekt z archiwum firmy Digilentic.com oryginalnie zaimplementowany dla zestawu FPGA "Nexys Video" - oto link do projektu: https://projects.digilentinc.com/cc-ad/cmos-sensor-camera-system-9f74f8 Ja dostosowałem projekt do posiadanej przeze mnie płytki z FPGA Artix 7 firmy QMTECH ponieważ posiada ona wystarczająco dużą ilość pamięci BRAM do implementacji pełnego frame-bufora dla rozdzielczości VGA - oto link do tej płytki: https://www.aliexpress.com/item/4000170042795.html?spm=a2g0o.productlist.0.0.1bbc3a488cWayC&algo_pvid=b8e2d6de-11a7-4045-be1d-dc82c5229b85&algo_expid=b8e2d6de-11a7-4045-be1d-dc82c5229b85-3&btsid=39edaf33-09cc-4522-882b-0168a91a733d&ws_ab_test=searchweb0_0,searchweb201602_4,searchweb201603_55 Aby dostosować projekt do mojej płytki trzeba było dodać jeden IPcore "Clock Wizard" bo płytka Nexys Video miała zegar 100MHz a QMTECH 50 MHz. Poza tym sygnały Reset miały zanegowany poziom w stosunku do Nexys. Zmiena dwóch linii w pliku "top.v (70 i 71). Oryginalnie było: debounce_inputs #(.NR(1))dbi(CLK,~RESETn,RESETn_clean); debounce_inputs #(.NR(1))dbi_reset_test(CLK,~cam_RESETn,cam_RESETn_clean); Jest po zmianie: debounce_inputs #(.NR(1))dbi(CLK,RESETn,RESETn_clean); debounce_inputs #(.NR(1))dbi_reset_test(CLK,cam_RESETn,cam_RESETn_clean); Oczywiście cały plki "User constraints" (xdc) trzeba było dostosować do mojej płytki. Fazy syntezy i implementacji nawet kończyły się z niedużą ilością ostrzeżeń. Patrz zrzut ekranu: Projekt zadziałał (jest wykrywanie krawędzi) ale obraz dość mocno "smuży", na razie nie udało mi się ustalić co jest przyczyną (faktem jest że próby robiłem na bardzo małym monitorku z wejściem HDMI). Całość tak wygląda na zdjęciach: Zamieszczam w załączniku cały projekt dla płytki QMTECH dla Vivado HLS 2020.1 (właśnie przy okazji tego projektu zrobiłem upgrade Vivado do najnowszej wersji OS WIn10), może komuś się przyda. Odchudziłem projekt o trzy niepotrzebne fazy implementacji i teraz się zmieścił .CMOSCameraArtix7My.zip Pozdrawiam- 13 odpowiedzi

-

- 6

-

-

- FPGA

- CMOS camera

-

(i 1 więcej)

Tagi:

-

Cześć, dzisiaj wykonałem próbę podłączenia prostej kamery VGA (sensor CMOS) do zestawu FPGA firmy QMTECH z Artix-7 (chip FPGA: XC7A100T-2FGG677i). Tutaj jest link do tego zestawu: https://pl.aliexpress.com/item/4000170042795.html?spm=a2g0o.productlist.0.0.1bbc3a488cWayC&algo_pvid=b8e2d6de-11a7-4045-be1d-dc82c5229b85&algo_expid=b8e2d6de-11a7-4045-be1d-dc82c5229b85-3&btsid=39edaf33-09cc-4522-882b-0168a91a733d&ws_ab_test=searchweb0_0,searchweb201602_4,searchweb201603_55i Zestaw ten kupiłem jakiś czas temu i postanowiłem go użyć w tym projekcie ze względu na dużą ilość zasobów - szczególnie dużą ilość BRAM 4,660Kb (potrzebna na frame-buffer). Pewnie łatwiej i sensowniej byłoby podłączać jakąś kamerę z interfejsem MIPI (i lepszym sensorem), ale nie posiadam żadnego zestawu FPGA, który by miał wbudowany taki interfejs 😉 Jest to moja pierwsza próba podłączenia jakiejkolwiek kamery do zestawu FPGA. Wybrałem tanią kamerę "OV7670" (sensor firmy Omnivision) - tutaj link do sklepu (chińskiego): https://www.banggood.com/Wareshare-OV7670-Camera-Module-CMOS-Acquisition-Board-Adjustable-Focus-300000-Pixel-p-1478355.html?rmmds=search&cur_warehouse=CN Tutaj link do datasheet do tego sensora: https://www.voti.nl/docs/OV7670.pdf Wybrałem projekt ze strony "FPGA4Student" ponieważ z kilku branych pod uwagę wydał mi się najprostszy:był https://www.fpga4student.com/2018/08/basys-3-fpga-ov7670-camera.html Projekt był zrobiny dla zestawu FPGA "Basys 3" z Artixem-7 (XC7A35T-1CPG236C) który posiada tylko 1800 Kb wewnętrznej pamieci BRAM - stąd frame-buffer obsługuje tylko max. rozdzielczość 320x240. Można by go też odpalić na zestawach "Artix-7 35T Arty" lub "Digilent Cmod At-35T" - tutaj linki do tych zestawów: https://kamami.pl/zestawy-uruchomieniowe/560134-artix-7-35t-arty-zestaw-ewaluacyjny-dla-fpga-artix-7.html https://kamami.pl/zestawy-uruchomieniowe/562401-digilent-cmod-a7-35t-modul-uruchomieniowy-z-fpga-artix-7-410-328-35.html Ale wracając do projektu - moja płytka FPGA firmy QMTECH (XC7A100T) nie posiada wyjściowego interfejsu VGA (ma HDMI które wypróbowałem i które działa dobrze), stąd wynikła potrzeba zbudowania go samemu. Wybrałem prosty interfejs (12) rezystorów wzorując się na układzie z zestawu "Basys 3". Tutaj schemat tego interfejsu: Zmontowałem do na płytce prototypowej (potrzebne jest gniazdo VGA 15 pinowe). Tak wygląda cały układ z kamerą, interfejsem VGA (na zielonej płytce) i zestawem FPGA QMTECH. A tu obraz na monitorze (tylko składowa niebieska): Jak widzicie próba nie zakończyła się pełnym sukcesem obraz jest o rozdzielczości 320x240 pikseli (i tak miało być) natomiast jest widoczna na ekranie tylko składowa niebieska.Podejrzewam, że błąd jest na zielonej płytce z interfejsem VGA - bo była ona dzisiaj "na szybko" polutowana a nie była najpierw przetestowana (może pomyliłem się przy gnieździe VGA). Zamieszczam tu pełen projekt dla Vivado 2018.3. Plik constraints dla mojej płytki QMETCH, ale na oryginalnej stronie projektu mo\zna pobrać pełen projekt dla "Basys 3". basys3_ov7670_v1.zip W najbliższym czasie zamierzam usunąć błędy z interfejsu VGA oraz zwiększyć pojemność frame-buffer'a do pełnej rozdzielczości VGA (na mojej płytce powinno wystarczyć pamieci BRAM w układzie FPGA). Zamieszczam projekt, bo może ktoś będzie także chciał spróbować podłączyć taki model kamery do układu FPGA. Zachęcam wszystkich do własnych prób z układami FPGA, bo w dziale "Układy programowalne" na Forbocie ostatnio bardzo mało się dzieje. Pozdrawiam 🙂