Przeszukaj forum

Pokazywanie wyników dla tagów 'MimasV.2'.

Znaleziono 2 wyniki

-

Cześć, ponieważ, przy szukaniu kodu dla gry "Snake" natrafiłem na fajne repozytorium kodu dla płytki FPGA "Pepino" (Xilinx Spartan6), postanowiłem spróbować uruchomić jeszcze jedną "oldschool'ową" grę "Pacaman" na zestawie FPGA. W tym przypadku była wymaganą minimalna ilość pracy w kodzie projektu pobranego z repozytorium GIT(dla płytki Pepino): zamiana pliku "user constraints" "pacman.ucf". Tutaj prawidłowa postać tego pliku dla płytki Mimas V.2: # NUMATO Mimas V2 ucf file ## http://numato.com/ ## PACMAN UCF by Alex CONFIG VCCAUX = 3.3; ##Clock signal 100 MHz NET "SYS_CLK" LOC = V10 | IOSTANDARD = LVCMOS33 | PERIOD = 100MHz; NET "SYS_CLK" TNM_NET = "sys_clk_pin"; TIMESPEC TS_sys_clk_pin = PERIOD "sys_clk_pin" 100 MHz HIGH 50 %; # LEDS NET "LED[3]" LOC = P15 | IOSTANDARD = LVCMOS33 | DRIVE = 8 | SLEW = FAST; NET "LED[2]" LOC = U18 | IOSTANDARD = LVCMOS33 | DRIVE = 8 | SLEW = FAST; NET "LED[1]" LOC = T17 | IOSTANDARD = LVCMOS33 | DRIVE = 8 | SLEW = FAST; NET "LED[0]" LOC = T18 | IOSTANDARD = LVCMOS33 | DRIVE = 8 | SLEW = FAST; # DIP Switches for one player, two player and credit #DP 8 NET "SW[0]" LOC = C17 | IOSTANDARD = LVCMOS33 | DRIVE = 8 | SLEW = FAST | PULLUP; NET "SW[1]" LOC = C18 | IOSTANDARD = LVCMOS33 | DRIVE = 8 | SLEW = FAST | PULLUP; NET "SW[2]" LOC = D17 | IOSTANDARD = LVCMOS33 | DRIVE = 8 | SLEW = FAST | PULLUP; NET "SW[3]" LOC = D18 | IOSTANDARD = LVCMOS33 | DRIVE = 8 | SLEW = FAST | PULLUP; # Push Buttons Switches For Joystick #SW6 - FIRE NET "JOYSTICK[4]" LOC = P1 | IOSTANDARD = LVCMOS33 | DRIVE = 8 | SLEW = FAST | PULLUP; #SW1 RIGHT NET "JOYSTICK[3]" LOC = M18 | IOSTANDARD = LVCMOS33 | DRIVE = 8 | SLEW = FAST | PULLUP; #SW2 LEFT NET "JOYSTICK[2]" LOC = L18 | IOSTANDARD = LVCMOS33 | DRIVE = 8 | SLEW = FAST | PULLUP; #SW1 DOWN NET "JOYSTICK[1]" LOC = L17 | IOSTANDARD = LVCMOS33 | DRIVE = 8 | SLEW = FAST | PULLUP; #SW3 UP NET "JOYSTICK[0]" LOC = M16 | IOSTANDARD = LVCMOS33 | DRIVE = 8 | SLEW = FAST | PULLUP; # Audio # # Audio Left NET "audio_l" LOC = B16 | IOSTANDARD = LVCMOS33 | DRIVE = 8 | SLEW = FAST; # Audio Right NET "audio_r" LOC = A16 | IOSTANDARD = LVCMOS33 | DRIVE = 8 | SLEW = FAST; # VGA Connections NET "VGA_HSYNC" LOC = B12 | IOSTANDARD = LVCMOS33 | DRIVE = 8 | SLEW = FAST; NET "VGA_VSYNC" LOC = A12 | IOSTANDARD = LVCMOS33 | DRIVE = 8 | SLEW = FAST; NET "VGA_RED[2]" LOC = C9 | IOSTANDARD = LVCMOS33 | DRIVE = 8 | SLEW = FAST; NET "VGA_RED[1]" LOC = B9 | IOSTANDARD = LVCMOS33 | DRIVE = 8 | SLEW = FAST; NET "VGA_RED[0]" LOC = A9 | IOSTANDARD = LVCMOS33 | DRIVE = 8 | SLEW = FAST; NET "VGA_GREEN[2]" LOC = C11 | IOSTANDARD = LVCMOS33 | DRIVE = 8 | SLEW = FAST; NET "VGA_GREEN[1]" LOC = A10 | IOSTANDARD = LVCMOS33 | DRIVE = 8 | SLEW = FAST; NET "VGA_GREEN[0]" LOC = C10 | IOSTANDARD = LVCMOS33 | DRIVE = 8 | SLEW = FAST; NET "VGA_BLUE[1]" LOC = A11 | IOSTANDARD = LVCMOS33 | DRIVE = 8 | SLEW = FAST; NET "VGA_BLUE[0]" LOC = B11 | IOSTANDARD = LVCMOS33 | DRIVE = 8 | SLEW = FAST; Poza tym trzeba było podmienić kawałek kodu w głównym entity projektu (związanego z głównym zegarem projektu) i dokonać zamiany typu układu FPGA Spartan6 (obudowa CSG324) we właściwościach projektu. No i dokonać syntezy i implementacji układu oraz generacji binarnego pliku konfiguracji układu FPGA ("pacman_top.bin" w katalogu "synth" projektu. Tutaj link do repozytorium kodu dla płytki FPGA Pepino (zawierającego miedzy innymi kod gry "Pacman"): https://github.com/Saanlima/Pepino/tree/master/Projects A tutaj link do tutoriala jakie zmiany trzeba wykonać, aby uruchomić grę "Pacman" na zestawie FPGA "Mimas V.2" (postępowałem dokladnie według tego tutorial'a): http://langster1980.blogspot.com/2016/04/pacman-running-on-mimas-v2-fpga.html Tak gra "Pacman prezentuje się na zestawie FPGA "Mimas V.2 (z małym monitorkiem 10 cali VGA): Myślę, że moim następnym krokiem będzie uruchomienie sprzętowego emulatora (na zestawie FPGA) komputera "Commodore C64" a w przyszłości "Amigi 600". No ale na to trzeba więcej czasu a i stopień skomplikowania projektu jest dużo większy. W archiwum zip spakowany projekt gry Pacman (dla Mimas V.2) dla "ISE 14.7" : Pepino-pacman.zip BTW: po namyśle, zdecydowałem, że "zabawę" z emulacją jakiejś prostej konsoli do gier rozpocznę od "NES" (Nintendo), bo w tym repozytorium dla płytki FPGA "Pepino" jest do jej emulacji fajny kod źródłowy: https://github.com/Saanlima/Pepino/tree/master/Projects/Pepino_NES_smb , tylko muszę najpierw kupić taki JoyPad (z oryginalnym złączem do konsoli NES) do tej konsoli (użyty w tym projekcie): https://allegro.pl/oferta/pad-do-konsoli-nintendo-entertainment-system-nes-11505068172 Pozdrawiam

-

Gra "Snake" na płytce FPGA "Mimas v.2" (Spartan6)

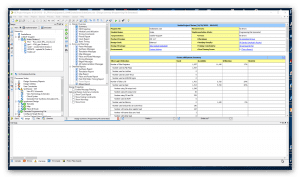

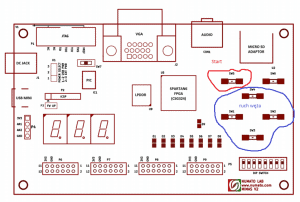

FlyingDutch opublikował temat w Układy programowalne

Cześć, ponieważ w ciągu tego roku byłem tak obciążony projektami elektronicznymi w pracy (i ich programowaniem), że nie mam w czasie wolnym ochoty na ambitne projekty. Ponieważ mam teraz kilka dni wolnych postanowiłem zająć się jakimś małym projektem, który da mi trochę rozrywki. Jak już kiedyś pisałem w latach 80-tych lubiłem grać w proste gry na "automatach", dlatego wybór padł znów na prostą grę "Snake"(wąż). Wybór padł na implementację tej gry na płytkę FPGA "Pepino" (także Spartan6) - niestety różni się sporo od Mimas V.2. Tutaj link do żródeł gry na Githgub'ie: https://github.com/Saanlima/Pepino/tree/master/Projects/Snake Przystępując do implementacji gry myślałem, że powinno udać się ją uruchomić na zestawie FPGA "Elbert V.2" (Spartan3) - niestety okazało się, iż liczba wymaganych zasobów jest ponad dwukrotnie większa od tej którą posiada ta płytka. Gra wymaga 1957 przerzutników (FF) i 1703 LUTs - patrz zrzut erranu z ISE: Tak, że mój wybór padł na zestaw FPGA "Mimas V.2", który posiadam od kilku lat. Tutaj linki do tego zestawu w Botland'zie oraz do producenta firmy "Numato Labs": https://botland.com.pl/moduly-i-zestawy-fpga/8603-mimas-v2-spartan-6-plytka-rozwojowa-fpga-5904422311964.html https://numato.com/product/mimas-v2-spartan-6-fpga-development-board-with-ddr-sdram/ https://numato.com/docs/mimas-v2-spartan-6-fpga-development-board-with-ddr-sdram/ Podstawową różnicą pomiędzy oryginalnym projektem na zestaw FPGA "Pepino" jest fakt, iż "Pepino" ma główny zegar 50 Mhz a Mimas v.2 100 Mhz. Poza tym ruch węża był realizowany poprzez klawiaturę PS2 podłączoną do plytki FPGA - ponieważ nie posiadam takiej klawiatury postanowiłem kontrolować ruch węża za pomocą przycisków na płytce Mimas. Z tego powodu można było usunąć dwa sygnały wejściowe: KB_clk i KB_data z głównego modułu aplikacji(Snake.v), i sam moduł obsługi klawiatury: kbInput(VGA_clk, KB_clk, KB_data, direction) Trzeba też było zmodyfikować plik "user constraints" (ucf) tak aby pasował do zestawu FPGA 'Mimas v.2". Oto lista wykonanych w projekcie zmian: 1) Zmodyfikowanie portów głównego modułu Snake.v: było: module Snake(start, master_clk, KB_clk, KB_data, VGA_R, VGA_G, VGA_B, VGA_hSync, VGA_vSync); input start; input master_clk, KB_clk, KB_data; output reg [2:0] VGA_R; output reg [2:0] VGA_G; output reg [1:0] VGA_B; output VGA_hSync, VGA_vSync; po modyfikacji: module Snake(start, clk100, VGA_R, VGA_G, VGA_B, VGA_hSync, VGA_vSync, btnUp, btnDown, btnLeft, btnRight); input start; input clk100; input btnUp, btnDown, btnLeft, btnRight; output reg [2:0] VGA_R; output reg [2:0] VGA_G; output reg [1:0] VGA_B; output VGA_hSync, VGA_vSync; 2) Usunięto moduł zegarowy w głównym module: // Use a CDM to generate VGA clock (25 MHz) from input clock (50 MHz) DCM #(.CLKIN_DIVIDE_BY_2("TRUE"), .CLKIN_PERIOD(20.000)) dcm(.CLKIN(master_clk), .CLKFB(VGA_clk), .RST(1'b0), .PSEN(1'b0), .PSINCDEC(1'b0), .PSCLK(1'b0), .DSSEN(1'b0), .CLK0(VGA_clk)); a dodano DCM (IPCore PLL_Clock), który teraz z zegara Mimas'a 100 MHz generuje dwa zegary (50 Mhz i 25 Mhz do taktowania modułu VGA): // Instantiate the module PLL_Clock PLL1 (// Clock in ports .CLK_IN1(clk100), // IN 100Mhz // Clock out ports .CLK_OUT1(master_clk), // OUT 50Mhz .CLK_OUT2(VGA_clk)); // OUT 25MHz 3) Usunięte zostało wywołanie modułu: kbInput i kod samego modułu: VGA_gen gen1(VGA_clk, xCount, yCount, displayArea, VGA_hSync, VGA_vSync); randomGrid rand1(VGA_clk, rand_X, rand_Y); //kbInput kbIn(VGA_clk, KB_clk, KB_data, direction); updateClk UPDATE(VGA_clk, update); module kbInput(VGA_clk, KB_clk, KB_data, direction); input VGA_clk; input KB_clk; input KB_data; output reg [3:0] direction = 4'b0000; reg Q0, Q1; reg [10:0] shreg; reg [7:0] code; wire endbit; assign endbit = ~shreg[0]; assign shift = Q1 & ~Q0; always @ (posedge VGA_clk) begin Q0 <= KB_clk; Q1 <= Q0; shreg <= (endbit) ? 11'h7FF : shift ? {KB_data, shreg[10:1]} : shreg; if (endbit) code <= shreg[8:1]; if(code == 8'h1D) direction <= 4'b0001; else if(code == 8'h1C) direction <= 4'b0010; else if(code == 8'h1B) direction <= 4'b0100; else if(code == 8'h23) direction <= 4'b1000; end endmodule zamiast tego został dodany fragment kodu obsługujący przyciski z płytki Mimas w module głównym (linie od 79 do 87): end else if (~game_over) begin if (update) begin for(count = 1; count < 128; count = count + 1) begin if(size > count) begin snakeX[count] <= snakeX[count - 1]; snakeY[count] <= snakeY[count - 1]; end end //obsluga przycisow z Mimasa if(btnDown == 1'b0) direction <= 4'b0001; else if(btnLeft == 1'b0) direction <= 4'b0010; else if(btnUp == 1'b0) direction <= 4'b0100; else if(btnRight == 1'b0) direction <= 4'b1000; case(direction) 4'b0001: snakeY[0] <= (snakeY[0] - 1); 4'b0010: snakeX[0] <= (snakeX[0] - 1); 4'b0100: snakeY[0] <= (snakeY[0] + 1); 4'b1000: snakeX[0] <= (snakeX[0] + 1); endcase Poniżej rysunek z przyciskami z Mimas'a użytymi do kontrolowania ruchu węża i gry: Przycisk SW5 to start nowej gry a przyciski:SW!, SW2, SW3, SW4 kontrolują ruch węża. Poniżej zdjęcie z gry uruchomionej na zestawie Mimas v.2 i małym monitorku VGA: Bym zapomniał: był jeszcze błąd języka Verilog w tym fragmencie kodu: module randomGrid(VGA_clk, rand_X, rand_Y); input VGA_clk; output reg [6:0] rand_X; output reg [6:0] rand_Y; always @(posedge VGA_clk) begin //rand_X <= ((rand_X + 3) % 78) + 1; //rand_Y <= ((rand_Y + 5) % 58) + 1; rand_X <= ((rand_X + 3) % 64) + 1; rand_Y <= ((rand_Y + 5) % 32) + 1; end endmodule dwie linie zostały wykomentowane i dodane dwie poniżej (zmienione) - Verilog wymaga, aby drugi argument operatora modulo % był potęgą liczby dwa. Tutaj plik "Snake.ucf" (z user constraints) dla płytki Mimas v.2: NET "*" IOSTANDARD=LVCMOS33; CONFIG VCCAUX = "3.3" ; # Clock 100 MHz NET "clk100" LOC = V10 | IOSTANDARD = LVCMOS33 | PERIOD = 100MHz ; NET "start" LOC = K17 | PULLUP; #SW5 # VGA port NET "VGA_hSync" LOC = B12; NET "VGA_vSync" LOC = A12; NET "VGA_R<0>" LOC = A9; NET "VGA_R<1>" LOC = B9; NET "VGA_R<2>" LOC = C9; NET "VGA_G<0>" LOC = C10; NET "VGA_G<1>" LOC = A10; NET "VGA_G<2>" LOC = C11; NET "VGA_B<0>" LOC = B11; NET "VGA_B<1>" LOC = A11; # Przyciski Mimas V.2 NET "btnLeft" LOC = M18 | IOSTANDARD = LVCMOS33 | DRIVE = 8 | SLEW = FAST | PULLUP; #SW1 NET "btnRight" LOC = L18 | IOSTANDARD = LVCMOS33 | DRIVE = 8 | SLEW = FAST | PULLUP; #SW2 NET "btnDown" LOC = L17 | IOSTANDARD = LVCMOS33 | DRIVE = 8 | SLEW = FAST | PULLUP; #SW3 NET "btnUp" LOC = M16 | IOSTANDARD = LVCMOS33 | DRIVE = 8 | SLEW = FAST | PULLUP; #SW4 Zamieszczam spakowany projekt gry dla "ISE 14.7 Webpack": SnakeGame.zip Plik binarny do wgrania konfiguracji FPGA to "snake.bin" (jeśli ktoś nie jest zainteresowany kodem źródłowym). Pozdrawiam