Przeszukaj forum

Pokazywanie wyników dla tagów 'LVDS'.

Znaleziono 3 wyniki

-

Cześć, ostatnio przeglądam sobie alternatywy dla RP CM4 i znalazłem coś takiego. Czy ktoś jest w stanie mi powiedzieć czy do tego mistycznego LVDS "Dual Flatlink 1920×1080 24-bit" dam radę podłączyć jakąś typową matrycę od laptopa (oczywiście pod LVDS, a nie pod eDP 😉). Z tego co widzę matryca ma 2 kanały 8 bit... Więc ciężko stwierdzić, gdyż nie jestem ekspertem w temacie tego standardu (a raczej nawet podstaw nie mam). Alternatywnie raczej pozostanę przy CM4 i wyprowadzeniu HDMI. EDIT: Nvm, udało mi się dokopać do danych w dokumentacji i raczej da radę, tylko muszę jeszcze dwa razy policzyć piny (bo nikt łaskawie nie opisał ile jest pinów od LVDS w złączu 😞)

-

Posiadam kamerę Sony FCB-EV7520 (dokumentacja w załączniku), której wyjściem wideo jest sygnał w postaci YPbPr 4:2:2 wysyłany za pomocą interfejsu LVDS. To czego potrzebuje to napisanie programu na układ FPGA, który odbierze sygnał LVDS, przekształci go i wypuści sygnał zgodny ze standardem HDMI lub USB. Nie jest to coś nowego, bo tego typu urządzenia są w sprzedaży, lecz są drogie 350€ i mają już konkretny kształt, a w przyszłości chciałbym móc to zamknąć na swojej PCB. Jeżeli masz doświadczenie z FPGA, szczególnie z przetwarzaniem wyżej wymienionych sygnałów wideo to zapraszam do kontaktu. Jestem zainteresowany kompleksowym rozwiązaniem, ale również jestem otwarty na współpracę na zasadzie wskazania kierunku, zasugerowania możliwego rozwiązania i pomocy w wyborze odpowiedniego sprzętu. FCB-EV7520_Manual.pdf 22_FCB-EV7520A_S.pdf

-

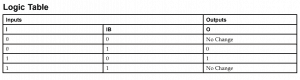

W ramach pewnego projektu muszę obsłużyć komunikację za pomocą interfejsu LVDS w układzie programowalnym FPGA (lub w zasadzie, w tej chwili, SoC). Interesuje mnie zarówno nadajnik, jak również odbiornik. Szukam materiałów na ten temat w internecie i w zasadzie jedyne co znalazłem to odpowiednie skonfigurowanie pinów i użycie prymitywów (np. IBUFDS - dla Xilinxa) w kodzie VHDL (tego języka używam). Czy jest jakaś (w miarę prosta) możliwość zastąpienia tych prymitywów własnym kodem? Nie mam pomysłu na napisanie takiego elementu, niewprowadzającego zbędnych opóźnień. Zależy mi na zapewnieniu możliwie jak największej „przenoszalności" kodu. Czy jest możliwość sprawdzenia, co tak naprawdę znajduje się w tych prymitywach (chciałbym zobaczyć, co „siedzi" w środku)? Czy może jest to po prostu fizyczny element, „zaszyty" wewnątrz FPGA? Czy jeżeli opiszę własny komponent, mający dwa wejścia (sygnały różnicowe zanegowany i nie) i jedno wyjście (które będzie po prostu podłączone do wejścia niezanegowanego lub będzie działać według załączonej tabeli zaczerpniętej z dokumentacji Xilinxa), to narzędzie do syntezy „domyśli się", że trzeba wstawić w to miejsce wejściowy bufor różnicowy? Czy nie będzie problemu z przeniesieniem projektu na inny układ (innego producenta)? Przepraszam za poziom pytań, ale pierwszy raz będę korzystał z transmisji różnicowej i nie wszystko jest dla mnie jasne. Ponadto, nie mam dużego doświadczenia z układami programowalnymi.