Przeszukaj forum

Pokazywanie wyników dla tagów 'FPGA'.

Znaleziono 29 wyników

-

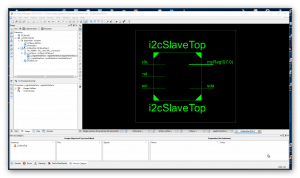

Chciałbym zaprosić wszystkich zainteresowanych do mojego kursu FPGA Lattice w języku Verilog. W kursie wykorzystujemy FPGA typu MachXO2 z uwagi na jego niską cenę, obudowę łatwą do lutowania i duży potencjał w wykorzystaniu na potrzeby hobbystycznych projektów. Kurs jest publikowany w Elektronice Praktycznej, a także dostępny jest na stronie ep.com.pl. Wszystkie odcinki starsze niż 3 miesiące dostępne są bezpłatnie. Wciąż piszę kolejne odcinki i co miesiąc będzie pojawiać się kolejny. Będę wdzięczny za wszystkie uwagi i sugestie, a także propozycje tematów do kolejnych odcinków kursu. Repozytorium modułów używanych w kursie Tutaj znajdują się różne moduły wraz z opisem oraz z testbenchami. Kurs jest zorganizowany w taki sposób, że moduły opracowane w poprzednich odcinkach kursu (jak np. sterownik wyświetlacza) są wykorzystywane później w bardziej zaawansowanych odcinkach. Aby ułatwić dostęp do tych modułów wszystko jest opublikowane również na GitHubie. https://github.com/leonow32/verilog-fpga Płytki rozwojowe do kursu FPGA Lattice https://ep.com.pl/projekty/projekty-ep/15788-plytki-rozwojowe-do-kursu-fpga-lattice Niedrogi programator JTAG https://ep.com.pl/projekty/projekty-ep/15365-niedrogi-programator-jtag-do-ukladow-fpga Wszystkie odcinki kursu: EP 2022/11 - Wstęp EP 2022/12 - Pierwszy projekt EP 2023/01 - Podstawy języka Verilog EP 2023/02 - Generator, dzielnik i licznik EP 2023/03 - IP Express i inne gotowce EP 2023/04 - Parametry i ćwiczenia EP 2023/05 - Analizator logiczny Reveal EP 2023/06 - Symulacja w EDA Playground EP 2023/07 - Wyświetlacz LED multipleksowany EP 2023/08 - Klawiatura matrycowa i maszyna stanów EP 2023/09 - Statyczna analiza czasowa i maksymalna częstotliwość zegara EP 2023/10 - Symulacja w Icarus Verilog i GTK Wave EP 2023/11 - Wyświetlacz LCD multipleksowany EP 2023/12 - Enkoder obrotowy EP 2024/01 - Pamięć EBR EP 2024/02 - Generowanie dźwięków EP 2024/03 - Odtwarzacz melodii EP 2024/04 - Nadajnik UART EP 2024/05 - Odbiornik UART EP 2024/06 - 14-segmentowy wyświetlacz LCD EP 2024/07 - Terminal UART z 14-segmentowym wyświetlaczem LCD EP 2024/08 - Sekwencyjny algorytm Double Dabble EP 2024/09 - Kombinacyjny algorytm Double Dabble Będę wdzięczny za wszystkie uwagi i sugestie, a także propozycje tematów do kolejnych odcinków kursu.

-

Cześć, próbował może ktoś z użytkowników forum tworzyć własne moduły biblioteczne i pakować je jako "IP Core" w Xilinx Vivado? Chodzi mi głównie o tworzenie większych modułów z wykorzystaniem magistrali AXI (zarówno Stream, jak i Memory Mapped), bo raczej bez wykorzystania tej magistrali, nie da się za dużo zrobić w technologii Xilinx'a. Chodzi mi o tworzenie własnych "IP Core's" zarówno jako RTL (języki: VHDL i Verilog"), jak i za pomocą HLS (w języku C++). Możecie polecić jakieś dobre tutoriale związane z tym zagadnieniem? Pozdrawiam

-

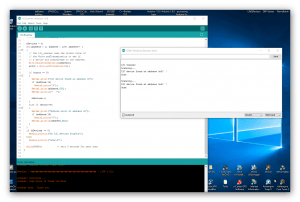

Witam serdecznie! Osoby, które chciałyby zainstalować środowisko ISE Xilinx w wersji 14.7, np. tak jak to jest opisane w Kursie FPGA, mogą napotkać następujący problem: przy próbie otwarcia jakiegokolwiek pliku, już w czasie instalacji licencji - po kliknięciu przycisku "Load License..." w Xilinx License Configuration Manager, czy później już w czasie używania aplikacji ISE Design Suite przy próbie otwarcia pliku .vhd - aplikacja zamyka się bez żadnego komunikatu - po prostu okienko znika bez śladu... Chwilę mi zajęło znalezienie rozwiązania tego problemu, ale ostatecznie udało się go rozwiązać, więc może podzielę się tutaj tą informacją z nadzieją, że dzięki temu ktoś zaoszczędzi kilka minut googlania... 😉 1) W samym Xilinx License Configuration Managerze rozwiązanie jest proste - zamiast klikać "Load License..." wystarczy wpisać ścieżkę do pliku z licencją w polu opisanym "XILINXD_LICENSE_FILE", a następnie kliknąć przycisk "Set". 2) Aby "naprawić" ISE Design Suite trzeba podmienić plik libPortability.dll znajdujący się w folderze ...\Xilinx\14.7\ISE_DS\ISE\lib\nt64 (gdzie "..." oznacza tutaj miejsce, gdzie znajduje się folder Xilinx z zainstalowanym środowiskiem - np. C:\) oraz w folderze ...\Xilinx\14.7\ISE_DS\common\lib\nt64 plikiem libPortabilityNOSH.dll, który znajduje się w folderze ...\Xilinx\14.7\ISE_DS\ISE\lib\nt64. Czyli np. zmieniamy nazwy plików libPortability.dll na libPortability.dll.backup, robimy kopię pliku libPortabilityNOSH.dll z tego pierwszego folderu, nadajemy jej nazwę libPortability.dll, a następnie umieszczamy tak spreparowany plik w obu w.w. folderach. Oczywiście opisaną tu operację robić należy przy zamkniętych wszystkich aplikacjach ze środowiska Xilinx. Rozwiązanie opisane wyżej wydedukowałem z tego wpisu na stronie Xilinx.com. Wprawdzie problem tam opisywany był trochę inny, a wyżej opisana metoda stanowiła tylko część tego rozwiązania, które tam się pojawiło, ale jej zastosowanie w moim przypadku dało dobry rezultat (przynajmniej na ten moment nie widzę już problemów - udało mi się utworzyć projekt, napisać moduł VHDL, utworzyć na jego podstawie plik binarny do zaprogramowania FPGA i wgrać ten plik na płytkę). Pozdrowienia dla wszystkich fanów układów programowalnych! 🙂

- 4 odpowiedzi

-

- 3

-

-

- Xilinx

- Windows 10

-

(i 2 więcej)

Tagi:

-

Zestaw uruchomieniowy na FPGA Gowin serii GW1N-9

FlyingDutch opublikował temat w Układy programowalne

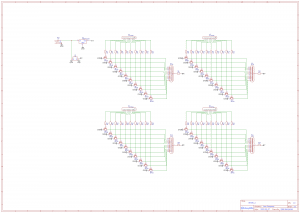

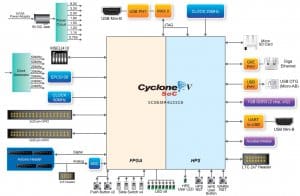

Cześć, już od jakiegoś czasu myślę nad własnym zestawem uruchomieniowym na układzie FPGA firmy Gowin. Postanowiłem ten zestaw oprzeć na układzie GW1N-LV9LQ144. Jest to układ zawierający 8640 LUT i 6480 Flip_Flop - patrz porównanie zasobów układów FPGA Gowin serii GW1N: https://www.gowinsemi.com/en/product/detail/46/ Dzięki temu na tym zestawie będzie można wypróbować Soft-CPU (np. z rodziny RISC-V) oraz bardziej skomplikowane IP Cores firmy Gowin: https://www.gowinsemi.com/en/support/ip/ Dzisiaj miałem trochę czasu, aby usiąść nad tym projektem. Udało mi się zaprojektować układy potrzebne do setup'u Układu FPGA, zasilanie banków układu FPGA, układ USB 2 JTAG (układ będzie można programować przez programator JTAG oparty na układzie scalonym FT2232, oraz przez header JTAG). Pamieć RAM (PSRAM 8MB) i zewnętrzny SPI Flash. W dalszej części będę dodawał peryferia do tego zestawu FPGA: diody LED, DIP-Switch'e, switche, DAC VGA, czytnik kart uSD, przetwornik ADC i DAC. Zamieszczam początkowy schemat zestawu FPGA (który będę aktualizował). W przyszłości zamieszczę także projket płytki PCB dla tego zestawu. Schematic_Gowin_GW!N_LV9_LQ144_DevBoard_2023-04-30.pdf Zależało mi aby ten zestaw posiadał wewnętrzny programator JTAG (z portem USB), tak aby można go programować bez zewnętrznego programatora "Gowin cable", który jest drogi. Robiłem próby z pamięcią SRAM 2Mx16-bit i działa ona OK, ale jest bardzo droga, więc postanowiłem użyć dużo tańszej pamieci PSRAM (8 MB).Dodałem też zewnętrzny SPI Fash do zestawu. Pozdrawiam- 39 odpowiedzi

-

- 2

-

-

Cześć, postanowiłem dzisiaj wypróbować generację kodu VHDL z użyciem "chat GPT". Założenia były takie, że mamy tablicę (bufor obrazu) o rozdzielczości VGA (640x480 pikseli, gdzie kazdy piksel ma 16 bitów). Aby kod był niezależny od konkretnej kości FPGA załozyłem, że opis obrazu jest w tablicy języka VHDL: signal image : array(0 to 639, 0 to 479) of STD_LOGIC_VECTOR(15 downto 0); a obraz wyjściowy (krawędzie) są w tablicy: signal edge_buffer : array(0 to 639, 0 to 479) of STD_LOGIC; Jest to po to aby abstrahować od konkretnego miejsca przechowywania obrazu (bufor obrazu), który docelowo może być w pamięci BLOCK_RAM układu FPGA lub w zewnętrznej pamięci RAM. Na początku poprosiłem "chatGPT" o wygenerowanie prostego przykładu filtrowania obrazu filtrem Sobel'a. Kod został szybko wygenerowany i wydawał się być całkiem poprawny (porównałem podstawową implementację filtru Sobel'a w języku C++). Nastepnie prosiłem chatGPT o dodawanie kolejnych opcji zrównoleglania - po kolei: 1) Zrównoleglanie liczby jednocześnie przetwarzanych pikseli - stała: constant PARALLELISM : natural := 4; 2) Podział obrazu FPGA na bloki przetwarzane równolegle: constant NUM_BLOCKS_X : integer := 160; -- Ilość bloków pikseli w poziomie constant NUM_BLOCKS_Y : integer := 120; -- Ilość bloków pikseli w pionie 3) Dodanie pipeline do przetwarzania Tutaj cały wygenerowany kod VHDL: library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity SobelEdgeDetection is Port ( clk : in STD_LOGIC; reset : in STD_LOGIC; pixel_in : in STD_LOGIC_VECTOR(15 downto 0); edge_out : out STD_LOGIC ); end SobelEdgeDetection; architecture ParallelPipelinedBehavior of SobelEdgeDetection is type PixelBlock is array(0 to 3, 0 to 3) of STD_LOGIC_VECTOR(15 downto 0); signal block_x : integer := 0; signal block_y : integer := 0; signal image : array(0 to 639, 0 to 479) of STD_LOGIC_VECTOR(15 downto 0); signal edge_buffer : array(0 to 639, 0 to 479) of STD_LOGIC; signal sobel_x : integer; signal sobel_y : integer; signal gradient : integer; signal gradient_reg : integer := 0; constant sobel_mask_x : array(0 to 2, 0 to 2) of integer := ((-1, 0, 1), (-2, 0, 2), (-1, 0, 1)); constant sobel_mask_y : array(0 to 2, 0 to 2) of integer := ((-1, -2, -1), ( 0, 0, 0), ( 1, 2, 1)); constant NUM_BLOCKS_X : integer := 160; -- Ilość bloków pikseli w poziomie constant NUM_BLOCKS_Y : integer := 120; -- Ilość bloków pikseli w pionie constant PARALLELISM : natural := 4; signal processing_stage : integer := 0; signal sobel_x_stage : integer; signal sobel_y_stage : integer; signal gradient_stage : integer; signal edge_stage : STD_LOGIC; signal pipeline_ready : boolean := false; begin process(clk) begin if rising_edge(clk) then if reset = '1' then block_x <= 0; block_y <= 0; processing_stage <= 0; for i in 0 to 639 loop for j in 0 to 479 loop image(i, j) <= (others => '0'); edge_buffer(i, j) <= '0'; end loop; end loop; else -- Przetwarzanie równoległe z pipeliningiem if not pipeline_ready then case processing_stage is when 0 => -- Wczytywanie bloku pikseli for i in 0 to 3 loop for j in 0 to 3 loop image(block_x * 4 + i, block_y * 4 + j) <= pixel_in; end loop; end loop; if block_x = NUM_BLOCKS_X - 1 and block_y = NUM_BLOCKS_Y - 1 then pipeline_ready <= true; processing_stage <= 0; -- Reset etapu przetwarzania elsif block_x = NUM_BLOCKS_X - 1 then block_x <= 0; block_y <= block_y + 1; else block_x <= block_x + 1; end if; when 1 => -- Obliczenia gradientów sobel_x_stage <= (to_integer(unsigned(image(block_x * 4 - 1, block_y * 4 - 1))) * sobel_mask_x(0, 0)) + (to_integer(unsigned(image(block_x * 4, block_y * 4 - 1))) * sobel_mask_x(0, 1)) + (to_integer(unsigned(image(block_x * 4 + 1, block_y * 4 - 1))) * sobel_mask_x(0, 2)) + (to_integer(unsigned(image(block_x * 4 - 1, block_y * 4))) * sobel_mask_x(1, 0)) + (to_integer(unsigned(image(block_x * 4 + 1, block_y * 4))) * sobel_mask_x(1, 2)) + (to_integer(unsigned(image(block_x * 4 - 1, block_y * 4 + 1))) * sobel_mask_x(2, 0)) + (to_integer(unsigned(image(block_x * 4, block_y * 4 + 1))) * sobel_mask_x(2, 1)) + (to_integer(unsigned(image(block_x * 4 + 1, block_y * 4 + 1))) * sobel_mask_x(2, 2)); sobel_y_stage <= (to_integer(unsigned(image(block_x * 4 - 1, block_y * 4 - 1))) * sobel_mask_y(0, 0)) + (to_integer(unsigned(image(block_x * 4, block_y * 4 - 1))) * sobel_mask_y(0, 1)) + (to_integer(unsigned(image(block_x * 4 + 1, block_y * 4 - 1))) * sobel_mask_y(0, 2)) + (to_integer(unsigned(image(block_x * 4 - 1, block_y * 4))) * sobel_mask_y(1, 0)) + (to_integer(unsigned(image(block_x * 4 + 1, block_y * 4))) * sobel_mask_y(1, 2)) + (to_integer(unsigned(image(block_x * 4 - 1, block_y * 4 + 1))) * sobel_mask_y(2, 0)) + (to_integer(unsigned(image(block_x * 4, block_y * 4 + 1))) * sobel_mask_y(2, 1)) + (to_integer(unsigned(image(block_x * 4 + 1, block_y * 4 + 1))) * sobel_mask_y(2, 2)); gradient_stage <= abs(sobel_x_stage) + abs(sobel_y_stage); if gradient_stage > 1000 then edge_stage <= '1'; else edge_stage <= '0'; end if; processing_stage <= 2; -- Przejdź do etapu 2 when 2 => -- Wczytywanie wyników do bufora krawędzi edge_buffer(block_x * 4 + 3, block_y * 4 + 3) <= edge_stage; if block_x = NUM_BLOCKS_X - 1 and block_y = NUM_BLOCKS_Y - 1 then pipeline_ready <= false; -- Zakończenie przetwarzania bloku elsif block_x = NUM_BLOCKS_X - 1 then block_x <= 0; block_y <= block_y + 1; else block_x <= block_x + 1; end if; end case; end if; end if; end if; end process; end ParallelPipelinedBehavior; Co sądzicie o wygenerowanym kodzie - wstepnie go przeanalizowałem i na rzaie nie mogę znaleźć błędu. Co sądzicie ogólnie o generacji kodu w róznych językach programowania za pomocą "chatGPT" i ogólnie AI. Tutaj link do dużo potężniejszego narzędzia AI o nazwie kodowej "Gorilla" : https://lablab.ai/tech/gorilla Projekt "Gorilla" można za darmo testować na "Google Clolab". Pozdrawiam

-

Cześć, trafiłem na kolejny wart polecenia kompletny kurs języka Verilog (w języku angielskim). Tutaj link do całej serii na Youtube: https://www.youtube.com/watch?v=33PAoJGm2Fo&list=PL_3xKnVkfI2itQhCyfnamNYSCHd2KHi4k&index=1 Pozdrawiam

-

Cześć, ponieważ, przy szukaniu kodu dla gry "Snake" natrafiłem na fajne repozytorium kodu dla płytki FPGA "Pepino" (Xilinx Spartan6), postanowiłem spróbować uruchomić jeszcze jedną "oldschool'ową" grę "Pacaman" na zestawie FPGA. W tym przypadku była wymaganą minimalna ilość pracy w kodzie projektu pobranego z repozytorium GIT(dla płytki Pepino): zamiana pliku "user constraints" "pacman.ucf". Tutaj prawidłowa postać tego pliku dla płytki Mimas V.2: # NUMATO Mimas V2 ucf file ## http://numato.com/ ## PACMAN UCF by Alex CONFIG VCCAUX = 3.3; ##Clock signal 100 MHz NET "SYS_CLK" LOC = V10 | IOSTANDARD = LVCMOS33 | PERIOD = 100MHz; NET "SYS_CLK" TNM_NET = "sys_clk_pin"; TIMESPEC TS_sys_clk_pin = PERIOD "sys_clk_pin" 100 MHz HIGH 50 %; # LEDS NET "LED[3]" LOC = P15 | IOSTANDARD = LVCMOS33 | DRIVE = 8 | SLEW = FAST; NET "LED[2]" LOC = U18 | IOSTANDARD = LVCMOS33 | DRIVE = 8 | SLEW = FAST; NET "LED[1]" LOC = T17 | IOSTANDARD = LVCMOS33 | DRIVE = 8 | SLEW = FAST; NET "LED[0]" LOC = T18 | IOSTANDARD = LVCMOS33 | DRIVE = 8 | SLEW = FAST; # DIP Switches for one player, two player and credit #DP 8 NET "SW[0]" LOC = C17 | IOSTANDARD = LVCMOS33 | DRIVE = 8 | SLEW = FAST | PULLUP; NET "SW[1]" LOC = C18 | IOSTANDARD = LVCMOS33 | DRIVE = 8 | SLEW = FAST | PULLUP; NET "SW[2]" LOC = D17 | IOSTANDARD = LVCMOS33 | DRIVE = 8 | SLEW = FAST | PULLUP; NET "SW[3]" LOC = D18 | IOSTANDARD = LVCMOS33 | DRIVE = 8 | SLEW = FAST | PULLUP; # Push Buttons Switches For Joystick #SW6 - FIRE NET "JOYSTICK[4]" LOC = P1 | IOSTANDARD = LVCMOS33 | DRIVE = 8 | SLEW = FAST | PULLUP; #SW1 RIGHT NET "JOYSTICK[3]" LOC = M18 | IOSTANDARD = LVCMOS33 | DRIVE = 8 | SLEW = FAST | PULLUP; #SW2 LEFT NET "JOYSTICK[2]" LOC = L18 | IOSTANDARD = LVCMOS33 | DRIVE = 8 | SLEW = FAST | PULLUP; #SW1 DOWN NET "JOYSTICK[1]" LOC = L17 | IOSTANDARD = LVCMOS33 | DRIVE = 8 | SLEW = FAST | PULLUP; #SW3 UP NET "JOYSTICK[0]" LOC = M16 | IOSTANDARD = LVCMOS33 | DRIVE = 8 | SLEW = FAST | PULLUP; # Audio # # Audio Left NET "audio_l" LOC = B16 | IOSTANDARD = LVCMOS33 | DRIVE = 8 | SLEW = FAST; # Audio Right NET "audio_r" LOC = A16 | IOSTANDARD = LVCMOS33 | DRIVE = 8 | SLEW = FAST; # VGA Connections NET "VGA_HSYNC" LOC = B12 | IOSTANDARD = LVCMOS33 | DRIVE = 8 | SLEW = FAST; NET "VGA_VSYNC" LOC = A12 | IOSTANDARD = LVCMOS33 | DRIVE = 8 | SLEW = FAST; NET "VGA_RED[2]" LOC = C9 | IOSTANDARD = LVCMOS33 | DRIVE = 8 | SLEW = FAST; NET "VGA_RED[1]" LOC = B9 | IOSTANDARD = LVCMOS33 | DRIVE = 8 | SLEW = FAST; NET "VGA_RED[0]" LOC = A9 | IOSTANDARD = LVCMOS33 | DRIVE = 8 | SLEW = FAST; NET "VGA_GREEN[2]" LOC = C11 | IOSTANDARD = LVCMOS33 | DRIVE = 8 | SLEW = FAST; NET "VGA_GREEN[1]" LOC = A10 | IOSTANDARD = LVCMOS33 | DRIVE = 8 | SLEW = FAST; NET "VGA_GREEN[0]" LOC = C10 | IOSTANDARD = LVCMOS33 | DRIVE = 8 | SLEW = FAST; NET "VGA_BLUE[1]" LOC = A11 | IOSTANDARD = LVCMOS33 | DRIVE = 8 | SLEW = FAST; NET "VGA_BLUE[0]" LOC = B11 | IOSTANDARD = LVCMOS33 | DRIVE = 8 | SLEW = FAST; Poza tym trzeba było podmienić kawałek kodu w głównym entity projektu (związanego z głównym zegarem projektu) i dokonać zamiany typu układu FPGA Spartan6 (obudowa CSG324) we właściwościach projektu. No i dokonać syntezy i implementacji układu oraz generacji binarnego pliku konfiguracji układu FPGA ("pacman_top.bin" w katalogu "synth" projektu. Tutaj link do repozytorium kodu dla płytki FPGA Pepino (zawierającego miedzy innymi kod gry "Pacman"): https://github.com/Saanlima/Pepino/tree/master/Projects A tutaj link do tutoriala jakie zmiany trzeba wykonać, aby uruchomić grę "Pacman" na zestawie FPGA "Mimas V.2" (postępowałem dokladnie według tego tutorial'a): http://langster1980.blogspot.com/2016/04/pacman-running-on-mimas-v2-fpga.html Tak gra "Pacman prezentuje się na zestawie FPGA "Mimas V.2 (z małym monitorkiem 10 cali VGA): Myślę, że moim następnym krokiem będzie uruchomienie sprzętowego emulatora (na zestawie FPGA) komputera "Commodore C64" a w przyszłości "Amigi 600". No ale na to trzeba więcej czasu a i stopień skomplikowania projektu jest dużo większy. W archiwum zip spakowany projekt gry Pacman (dla Mimas V.2) dla "ISE 14.7" : Pepino-pacman.zip BTW: po namyśle, zdecydowałem, że "zabawę" z emulacją jakiejś prostej konsoli do gier rozpocznę od "NES" (Nintendo), bo w tym repozytorium dla płytki FPGA "Pepino" jest do jej emulacji fajny kod źródłowy: https://github.com/Saanlima/Pepino/tree/master/Projects/Pepino_NES_smb , tylko muszę najpierw kupić taki JoyPad (z oryginalnym złączem do konsoli NES) do tej konsoli (użyty w tym projekcie): https://allegro.pl/oferta/pad-do-konsoli-nintendo-entertainment-system-nes-11505068172 Pozdrawiam

-

Cześć, chciałbym prosić o pomoc w kwestii podpięcia modułu Pmod BLE do płytki Zybo Z7-10. Opis projektu Chciałbym podłączyć Pmod BLE do płytki Zybo Z7-10. Chciałbym by testowa aplikacja mogła wysyłać i odbierać dane po bluetooth (do testowania chciałbym użyć jakiejś aplikacji z AppStore). Na początku mogłoby to być wysyłanie zwykłego ciągu znaków, jak np: "Cześć Zybo" i "Cześć telefon" czy coś podobnego. Próby podłączenia Znalazłem podobny przykład w intrnecie (tutaj -> link autorstwa osoby o nicku: ralphjy). Próbowałem odtworzyć projekt, który opisał w tym artykule jednak nie udało mi się to. Poniżej zamieszczam swój block diagram, który jest podobny do tego który prezentuje ralphjy. Dołączam jeszcze constraints mojego projektu. Niestety nie wiem jak dokładnie powinny być one podpięte. Na końcu problemu zamieszczam link do constraint dla Zybo. Oczywiście próbowałem wygenerować bitstreama, ale bezskutecznie :(. Może ktoś z Was miał już do czynienia z modułem Pmod BLE i byłby w stanie pomóc :)? Btw. dzięki wielkie za jakiekolwiek wskazówki! Sprzęt Zybo Z7-10 -> link Pmod BLE -> link Software Zybo-Z7 Constraints -> link pliki źródłowe Pmod BLE-> link

-

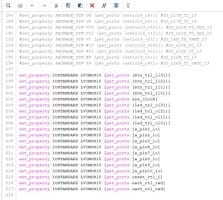

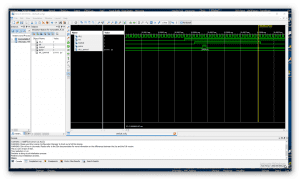

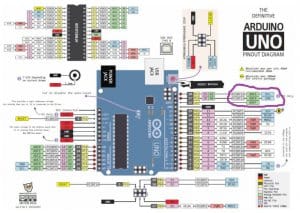

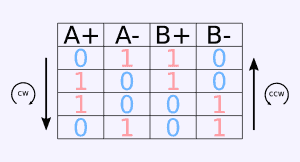

Cześć, jestem w trakcie prac nad zbieraniem sampli sygnału audio na zestawie FPGA "Sipeed Tang Nano 4K" i potrzebuje w celu debugowania układu jakiegoś kanału do komunikacji z portem szeregowym, lub Arduino. Chciałem użyć któregoś z IP Cores z "Gowin EDA" ale zarówno UART jak i "SPI Master" są tak przekombinowane, że ich użycie wymaga napisania sporej ilości kodu. Postanowiłem więc użyć zestawu FPGA "Elbert v.2" w celu napisania prostego kodu do komunikacji za pomocą protokołu SPI . Powstał więc bardzo prosty "SPI Master", który jest uruchomiony na zestawie FPGA i połączony za pomocą protokołu SPI z "Arduino UNO", które odbiera dane i wyświetla je za pomocą "Monitora portu szeregowego". Do samego kodu "SPI Master'a" został dołączony "debouncer" do przycisku i generator pojedynczego impulsu (o długości okresu zegara), który inicjuje wysłanie jednego bajtu danych. W celu wygenerowania jednego bardzo krótkiego impulsu napisałem (za pomocą kilku przerzutników typu D) i bramki AND układ generatora monostabilnego. Tutaj wynik symulacji działania generatora monostabilnego: Układ działa w ten sposób, że naciśnięcie przycisku (SW1 z Elbert'a) powoduje wysłanie jednego bajtu danych do Arduino za pomocą SPI. Tak wygląda układ testowy (potrzebny był poza FPGA i Arduino 4-liniowy konwerter poziomów logicznych): Tutaj kod w VHDL głównego modułu (a właściwie entity) projektu - plik "lw_spi_master.vhd ": library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; -- Uncomment the following library declaration if using -- arithmetic functions with Signed or Unsigned values --use IEEE.NUMERIC_STD.ALL; -- Uncomment the following library declaration if instantiating -- any Xilinx primitives in this code. --library UNISIM; --use UNISIM.VComponents.all; entity lw_spi_master is generic ( c_clkfreq : integer := 12_000_000; c_sclkfreq : integer := 5_000_000; c_cpol : std_logic := '0'; c_cpha : std_logic := '0' ); Port ( clk_i : in STD_LOGIC; en_i_Low : in STD_LOGIC; mosi_data_i : in STD_LOGIC_VECTOR (7 downto 0); miso_data_o : out STD_LOGIC_VECTOR (7 downto 0); data_ready_o : out STD_LOGIC; cs_o : out STD_LOGIC; sclk_o : out STD_LOGIC; mosi_o : out STD_LOGIC; miso_i : in STD_LOGIC ); end lw_spi_master; architecture Behavioral of lw_spi_master is component debounce is port ( clk : IN STD_LOGIC; --input clock button : IN STD_LOGIC; --input signal to be debounced result : OUT STD_LOGIC); --debounced signal end component; component monostable_ff is port( mono_pulse : out std_logic; clk : in std_logic; reset: in std_logic; key :in std_logic ); end component; signal write_reg : std_logic_vector (7 downto 0) := (others => '0'); signal read_reg : std_logic_vector (7 downto 0) := (others => '0'); signal en_i : std_logic := '0'; signal sclk_en : std_logic := '0'; signal sclk : std_logic := '0'; signal sclk_prev : std_logic := '0'; signal sclk_rise : std_logic := '0'; signal sclk_fall : std_logic := '0'; signal pol_phase : std_logic_vector (1 downto 0) := (others => '0'); signal mosi_en : std_logic := '0'; signal miso_en : std_logic := '0'; signal en_i_DB : std_logic; signal cnt : std_logic_vector (10 downto 0) := (others => '0'); constant c_edgecntrlimdiv2 : integer := c_clkfreq/(c_sclkfreq*2); signal edgecntr : integer range 0 to c_edgecntrlimdiv2 := 0; signal cntr : integer range 0 to 15 := 0; signal small_cnt : integer range 0 to 1000 := 0; signal blokada : integer range 0 to 3 := 0; type states is (S_IDLE, S_TRANSFER); signal state : states := S_IDLE; -------------------------------------------------------------------------------- -------------------------------------------------------------------------------- -------------------------------------------------------------------------------- begin C1: debounce port map (clk_i,en_i_Low, en_i_DB); C2: monostable_ff port map ( mono_pulse => en_i, clk => clk_i, reset => '1', key => not en_i_DB ); --en_i <= not(en_i_DB); pol_phase <= c_cpol & c_cpha; P_SAMPLE_EN : process (pol_phase, sclk_fall, sclk_rise) begin case pol_phase is when "00" => mosi_en <= sclk_fall; miso_en <= sclk_rise; when "01" => mosi_en <= sclk_rise; miso_en <= sclk_fall; when "10" => mosi_en <= sclk_rise; miso_en <= sclk_fall; when "11" => mosi_en <= sclk_fall; miso_en <= sclk_rise; when others => end case; end process; P_RISEFALL_DETECT : process (sclk, sclk_prev) begin if (sclk = '1' and sclk_prev = '0') then sclk_rise <= '1'; else sclk_rise <= '0'; end if; if (sclk = '0' and sclk_prev = '1') then sclk_fall <= '1'; else sclk_fall <= '0'; end if; end process; P_MAIN : process (clk_i) begin if (rising_edge(clk_i)) then sclk_prev <= sclk; case state is when S_IDLE => cs_o <= '1'; mosi_o <= '0'; data_ready_o <= '0'; sclk_en <= '0'; cntr <= 0; if (c_cpol = '0') then sclk_o <= '0'; else sclk_o <= '1'; end if; if (en_i = '1') then state <= S_TRANSFER; sclk_en <= '1'; write_reg <= mosi_data_i; mosi_o <= mosi_data_i(7); read_reg <= x"00"; end if; when S_TRANSFER => cs_o <= '0'; mosi_o <= write_reg(7); if (c_cpha = '1') then if (cntr = 0) then sclk_o <= sclk; if (miso_en = '1') then read_reg(0) <= miso_i; read_reg(7 downto 1) <= read_reg(6 downto 0); cntr <= cntr + 1; end if; elsif (cntr = 8) then data_ready_o <= '1'; miso_data_o <= read_reg; if (mosi_en = '1') then data_ready_o <= '0'; if (en_i = '1') then write_reg <= mosi_data_i; mosi_o <= mosi_data_i(7); sclk_o <= sclk; cntr <= 0; else state <= S_IDLE; cs_o <= '1'; end if; end if; elsif (cntr = 9) then if (miso_en = '1') then state <= S_IDLE; cs_o <= '1'; end if; else sclk_o <= sclk; if (miso_en = '1') then read_reg(0) <= miso_i; read_reg(7 downto 1) <= read_reg(6 downto 0); cntr <= cntr + 1; end if; if (mosi_en = '1') then mosi_o <= write_reg(7); write_reg(7 downto 1) <= write_reg(6 downto 0); end if; end if; else -- c_cpha = '0' if (cntr = 0) then sclk_o <= sclk; if (miso_en = '1') then read_reg(0) <= miso_i; read_reg(7 downto 1) <= read_reg(6 downto 0); cntr <= cntr + 1; end if; elsif (cntr = 8) then data_ready_o <= '1'; miso_data_o <= read_reg; sclk_o <= sclk; if (mosi_en = '1') then data_ready_o <= '0'; if (en_i = '1') then write_reg <= mosi_data_i; mosi_o <= mosi_data_i(7); cntr <= 0; else cntr <= cntr + 1; end if; if (miso_en = '1') then state <= S_IDLE; cs_o <= '1'; end if; end if; elsif (cntr = 9) then if (miso_en = '1') then state <= S_IDLE; cs_o <= '1'; end if; else sclk_o <= sclk; if (miso_en = '1') then read_reg(0) <= miso_i; read_reg(7 downto 1) <= read_reg(6 downto 0); cntr <= cntr + 1; end if; if (mosi_en = '1') then write_reg(7 downto 1) <= write_reg(6 downto 0); end if; end if; end if; end case; end if; end process; P_SCLK_GEN : process (clk_i) begin if (rising_edge(clk_i)) then if (sclk_en = '1') then if edgecntr = c_edgecntrlimdiv2-1 then sclk <= not sclk; edgecntr <= 0; else edgecntr <= edgecntr + 1; end if; else edgecntr <= 0; if (c_cpol = '0') then sclk <= '0'; else sclk <= '1'; end if; end if; end if; end process; end Behavioral; W tym pliku jest zawarta cała implementacja "SPI Master'a". Widać też użycia komponentów "debouncer'a" i generatora monostabilnego. Tutaj kod "deuboncer'a": LIBRARY ieee; USE ieee.std_logic_1164.all; USE ieee.std_logic_unsigned.all; ENTITY debounce IS GENERIC( counter_size : INTEGER := 20); --counter size (19 bits gives 10.5ms with 50MHz clock) PORT( clk : IN STD_LOGIC; --input clock button : IN STD_LOGIC; --input signal to be debounced result : OUT STD_LOGIC); --debounced signal END debounce; ARCHITECTURE logic OF debounce IS SIGNAL flipflops : STD_LOGIC_VECTOR(1 DOWNTO 0); --input flip flops SIGNAL counter_set : STD_LOGIC; --sync reset to zero SIGNAL counter_out : STD_LOGIC_VECTOR(counter_size DOWNTO 0) := (OTHERS => '0'); --counter output BEGIN counter_set <= flipflops(0) xor flipflops(1); --determine when to start/reset counter PROCESS(clk) BEGIN IF(clk'EVENT and clk = '1') THEN flipflops(0) <= button; flipflops(1) <= flipflops(0); If(counter_set = '1') THEN --reset counter because input is changing counter_out <= (OTHERS => '0'); ELSIF(counter_out(counter_size) = '0') THEN --stable input time is not yet met counter_out <= counter_out + 1; ELSE --stable input time is met result <= flipflops(1); END IF; END IF; END PROCESS; END logic; Tutaj kod VHDL generatora krótkiego impulsu "monostable_ff.vhd": library IEEE; use IEEE.STD_LOGIC_1164.ALL; entity monostable_ff is port( mono_pulse : out std_logic; clk : in std_logic; reset: in std_logic; key :in std_logic ); end monostable_ff; architecture Behavioral of monostable_ff is component DFF_AsyncReset is port( Q : out std_logic; QNot : out std_logic; clk : in std_logic; reset: in std_logic; D :in std_logic ); end component; component nand2 is port(a,b : in std_logic; y : out std_logic); end component; signal Q1,Q2,Q3,Q4,Q5 : std_logic; signal Q1N,Q2N,Q3N,Q4N,Q5N : std_logic; signal s11 : std_logic; begin DFF1: DFF_AsyncReset port map ( Q => Q1, QNot => Q1N, clk => clk, reset => reset, D => key ); DFF2: DFF_AsyncReset port map ( Q => Q2, QNot => Q2N, clk => clk, reset => reset, D => Q1 ); DFF3: DFF_AsyncReset port map ( Q => Q3, QNot => Q3N, clk => clk, reset => reset, D => Q2 ); DFF4: DFF_AsyncReset port map ( Q => Q4, QNot => Q4N, clk => clk, reset => reset, D => Q3 ); DFF5: DFF_AsyncReset port map ( Q => Q5, QNot => Q5N, clk => clk, reset => reset, D => Q4 ); mono_pulse <= (Q1 and Q5N); end Behavioral; Układ jest zrobiony na "liniI opóźniającej" z kilku przerzutników typu D i dwu-wejściowej bramki "AND" (kiedyś w mojej przeszłości budowało się podobne układy na układach scalonych z serii TTL). Do budowy tego generatora monostabilnego użyłem przerzutników typu D (wejście zegarowe reaguje na zbocze narastające) z asynchronicznym resetem stanem niskim. Tutaj kod przerzutnika typu D ---------------------------------------------------------------------------------- library IEEE; use IEEE.STD_LOGIC_1164.ALL; -- Uncomment the following library declaration if using -- arithmetic functions with Signed or Unsigned values --use IEEE.NUMERIC_STD.ALL; -- Uncomment the following library declaration if instantiating -- any Xilinx primitives in this code. --library UNISIM; --use UNISIM.VComponents.all; entity DFF_AsyncReset is port( Q : out std_logic; QNot : out std_logic; clk : in std_logic; reset: in std_logic; D :in std_logic ); end DFF_AsyncReset; architecture Behavioral of DFF_AsyncReset is begin process(clk,reset) begin if(reset='0') then Q <= '0'; QNot <= '1'; elsif(rising_edge(clk)) then Q <= D; QNot <= (not D); end if; end process; end Behavioral; A tutaj plik "user constraints" "lw-spi_master.ucf" dla zestawu Elbert v.2: CONFIG VCCAUX = "3.3" ; # Clock 12 MHz NET "clk_i" LOC = P129 | IOSTANDARD = LVCMOS33 | PERIOD = 12MHz; NET "en_i_Low" LOC = P80 | PULLUP | IOSTANDARD = LVCMOS33 | SLEW = SLOW | DRIVE = 12; #SW1 # mosi_data_i : in STD_LOGIC_VECTOR (7 downto 0); DIPSwitch NET "mosi_data_i[7]" LOC = P70 | PULLUP | IOSTANDARD = LVCMOS33 | SLEW = SLOW | DRIVE = 12; NET "mosi_data_i[6]" LOC = P69 | PULLUP | IOSTANDARD = LVCMOS33 | SLEW = SLOW | DRIVE = 12; NET "mosi_data_i[5]" LOC = P68 | PULLUP | IOSTANDARD = LVCMOS33 | SLEW = SLOW | DRIVE = 12; NET "mosi_data_i[4]" LOC = P64 | PULLUP | IOSTANDARD = LVCMOS33 | SLEW = SLOW | DRIVE = 12; NET "mosi_data_i[3]" LOC = P63 | PULLUP | IOSTANDARD = LVCMOS33 | SLEW = SLOW | DRIVE = 12; NET "mosi_data_i[2]" LOC = P60 | PULLUP | IOSTANDARD = LVCMOS33 | SLEW = SLOW | DRIVE = 12; NET "mosi_data_i[1]" LOC = P59 | PULLUP | IOSTANDARD = LVCMOS33 | SLEW = SLOW | DRIVE = 12; NET "mosi_data_i[0]" LOC = P58 | PULLUP | IOSTANDARD = LVCMOS33 | SLEW = SLOW | DRIVE = 12; # miso_data_o : out STD_LOGIC_VECTOR (7 downto 0); LEDs NET "miso_data_o[7]" LOC = P46 | IOSTANDARD = LVCMOS33 | SLEW = SLOW | DRIVE = 12; NET "miso_data_o[6]" LOC = P47 | IOSTANDARD = LVCMOS33 | SLEW = SLOW | DRIVE = 12; NET "miso_data_o[5]" LOC = P48 | IOSTANDARD = LVCMOS33 | SLEW = SLOW | DRIVE = 12; NET "miso_data_o[4]" LOC = P49 | IOSTANDARD = LVCMOS33 | SLEW = SLOW | DRIVE = 12; NET "miso_data_o[3]" LOC = P50 | IOSTANDARD = LVCMOS33 | SLEW = SLOW | DRIVE = 12; NET "miso_data_o[2]" LOC = P51 | IOSTANDARD = LVCMOS33 | SLEW = SLOW | DRIVE = 12; NET "miso_data_o[1]" LOC = P54 | IOSTANDARD = LVCMOS33 | SLEW = SLOW | DRIVE = 12; NET "miso_data_o[0]" LOC = P55 | IOSTANDARD = LVCMOS33 | SLEW = SLOW | DRIVE = 12; #################################################################################################### # HEADER P1 #################################################################################################### # sclk_o : out STD_LOGIC; NET "sclk_o" LOC = P31 | IOSTANDARD = LVCMOS33 | SLEW = FAST | DRIVE = 12; #1 # mosi_o : out STD_LOGIC; NET "mosi_o" LOC = P32 | IOSTANDARD = LVCMOS33 | SLEW = SLOW | DRIVE = 12; #2 # miso_i : in STD_LOGIC NET "miso_i" LOC = P28 | IOSTANDARD = LVCMOS33 | SLEW = SLOW | DRIVE = 12; #3 # cs_o : out STD_LOGIC; NET "cs_o" LOC = P30 | IOSTANDARD = LVCMOS33 | SLEW = SLOW | DRIVE = 12; #4 # data_ready_o : out STD_LOGIC; NET "data_ready_o" LOC = P27 | IOSTANDARD = LVCMOS33 | SLEW = SLOW | DRIVE = 12; #5 #Port ( # clk_i : in STD_LOGIC; # en_i_Low : in STD_LOGIC; # mosi_data_i : in STD_LOGIC_VECTOR (7 downto 0); # miso_data_o : out STD_LOGIC_VECTOR (7 downto 0); # data_ready_o : out STD_LOGIC; # cs_o : out STD_LOGIC; # sclk_o : out STD_LOGIC; # mosi_o : out STD_LOGIC; # miso_i : in STD_LOGIC #); Jak widać w pliku dane (bajt), które są wysyłane magistralą SPI do Arduino UNO, są podłączone do 8-miu DIP Switchy z zestawu Elbert, a przycisk "SW1" powoduje jednorazowa wysyłkę bajtu danych. Tutaj zrzut ekranu z "monitora portu szeregowego" z ARDUINO IDE z programem do odbioru danych po SPI.: Na koniec wklejam spakowany zip'em projekt dla Xilinx "ISE 14.7". Implementacja całego projektu zajmuje poniżej 100 LUT. Wklejam opis projektu bo takie funkcje komunikacyjne przydają się w przyszłości do bardziej skomplikowanych projektów. Teraz pozostaje uruchomienie kodu na zestawie FPGA "Sipeed Tang nano 4K". LW_SPI_master_01.zip Pozdrawiam

-

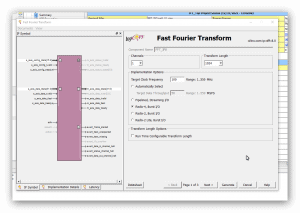

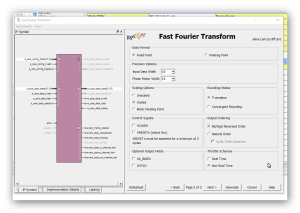

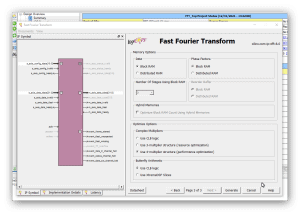

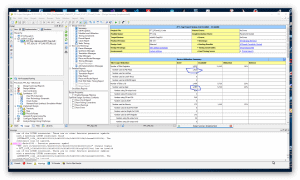

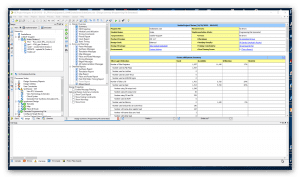

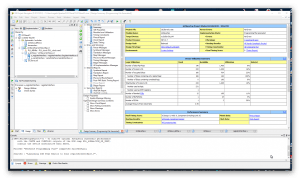

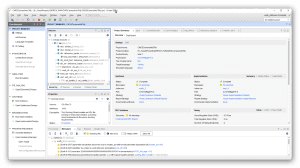

Cześć, jak wspomniałem wcześniej w wątku: Chciałbym porównać szybkość działania algorytmu FFT z użyciem "IP Core FFT" Xilinx'a. Mam zamiar wykonać próby na trzech zestawach FPGA (1024 próbki - 16 bit na próbkę - fixed point): 1) Elbert V.2 - Spartan3A (XC3S50A): brak bloków DSP i trzy sprzętowe układy mnożące 2) Mimas V.2 - Spartan6 (XC6SLX9) : 16 bloków DSP48 3) CMod A7-35 - Artix7 -(XC7A35T): 90 bloków DSP48 Z trzema różnymi częstotliwościami zegara układów FPGA. Rozpocząłem od projektu dla układu FPGA Spartan6(XC6SLX9 in CSG324 package) z zestawu MImas V.2: https://numato.com/product/mimas-v2-spartan-6-fpga-development-board-with-ddr-sdram/ Parametry IP Core FFT w wersji 8.0 Xilinx'a są tak dobrane tak, aby transformata FFT miała długość 1024 punkty i precyzję próbek 16-bit "fixed point" (z zegarem 100 MHz). Po ustawieniu parametrów IP Core jak jest przedstawione na kolejnych zrzutach ekranu: ekran 1 - długość transformaty 1024 punkty 1 kanał i opcja implementacji: "Radix-4, Burst I/O" (optymalizacja ze względu na czas wykonania(). ekran 2 - Precyzja 16-bit "scaled" ekran 3 - użycie "Block RAM", "Use 4-multipler structure" (optymalizacja z użyciem bloków DSP), "Arytmetyka Butterfly" z użyciem bloków CLB. Aby zorientować się jak działają konkretne wybrane opcje polecam przeczytać ten artykuł: https://www.allaboutcircuits.com/technical-articles/xilinx-fft-ip-core-fast-fourier-transform-software-walkthrough/ Po zakończeniu wyboru opcji dla "IP Core FFT V.8" i generacji jego modułów dodałem "top entity" (o nazwie: FFT_Top) w którym wywołuje(komponent) instancję IP Core FFT o nazwie " FFT_IP8". Na tym etapie jest to mi potrzebne wyłącznie w tym celu, aby móc uruchomić syntezę i implementację projektu w celu oszacowania liczby zasobów układu FPGA zużywanych przez projekt. I po zakończeniu fazy syntezy i implementacji można już podać liczbę podstawowych zużywanych zasobów: 1) Liczba przerzutników (FF) 1925 2) Liczba LUT 1468 3) Liczba użytych bloków DSP48 - 12 z 16 dostępnych (dla tej wersji układu Spartan6) Nie jest to mało - patrz zrzuty ekranu z ISE: Tutaj podaję kod głównego entity projektu (okazało się, że w przypadku tego IP Core jedyny wybór to język VHDL): ---------------------------------------------------------------------------------- -- Company: -- Engineer: -- -- Create Date: 13:32:16 12/31/2021 -- Design Name: -- Module Name: FFT_Top - Behavioral -- Project Name: -- Target Devices: -- Tool versions: -- Description: -- -- Dependencies: -- -- Revision: -- Revision 0.01 - File Created -- Additional Comments: -- ---------------------------------------------------------------------------------- library IEEE; use IEEE.STD_LOGIC_1164.ALL; -- Uncomment the following library declaration if using -- arithmetic functions with Signed or Unsigned values --use IEEE.NUMERIC_STD.ALL; -- Uncomment the following library declaration if instantiating -- any Xilinx primitives in this code. --library UNISIM; --use UNISIM.VComponents.all; entity FFT_Top is port ( aclk : in STD_LOGIC := 'X'; s_axis_config_tvalid : in STD_LOGIC := 'X'; s_axis_data_tvalid : in STD_LOGIC := 'X'; s_axis_data_tlast : in STD_LOGIC := 'X'; m_axis_data_tready : in STD_LOGIC := 'X'; s_axis_config_tready : out STD_LOGIC; s_axis_data_tready : out STD_LOGIC; m_axis_data_tvalid : out STD_LOGIC; m_axis_data_tlast : out STD_LOGIC; event_frame_started : out STD_LOGIC; event_tlast_unexpected : out STD_LOGIC; event_tlast_missing : out STD_LOGIC; event_status_channel_halt : out STD_LOGIC; event_data_in_channel_halt : out STD_LOGIC; event_data_out_channel_halt : out STD_LOGIC; s_axis_config_tdata : in STD_LOGIC_VECTOR ( 15 downto 0 ); s_axis_data_tdata : in STD_LOGIC_VECTOR ( 31 downto 0 ); m_axis_data_tdata : out STD_LOGIC_VECTOR ( 31 downto 0 ) ); end FFT_Top; architecture Behavioral of FFT_Top is ------------- Begin Cut here for COMPONENT Declaration ------ COMP_TAG COMPONENT FFT_IP8 PORT ( aclk : IN STD_LOGIC; s_axis_config_tdata : IN STD_LOGIC_VECTOR(15 DOWNTO 0); s_axis_config_tvalid : IN STD_LOGIC; s_axis_config_tready : OUT STD_LOGIC; s_axis_data_tdata : IN STD_LOGIC_VECTOR(31 DOWNTO 0); s_axis_data_tvalid : IN STD_LOGIC; s_axis_data_tready : OUT STD_LOGIC; s_axis_data_tlast : IN STD_LOGIC; m_axis_data_tdata : OUT STD_LOGIC_VECTOR(31 DOWNTO 0); m_axis_data_tvalid : OUT STD_LOGIC; m_axis_data_tready : IN STD_LOGIC; m_axis_data_tlast : OUT STD_LOGIC; event_frame_started : OUT STD_LOGIC; event_tlast_unexpected : OUT STD_LOGIC; event_tlast_missing : OUT STD_LOGIC; event_status_channel_halt : OUT STD_LOGIC; event_data_in_channel_halt : OUT STD_LOGIC; event_data_out_channel_halt : OUT STD_LOGIC ); END COMPONENT; -- COMP_TAG_END ------ End COMPONENT Declaration ------------ begin ------------- Begin Cut here for INSTANTIATION Template ----- INST_TAG FFT_1024_16 : FFT_IP8 PORT MAP ( aclk => aclk, s_axis_config_tdata => s_axis_config_tdata, s_axis_config_tvalid => s_axis_config_tvalid, s_axis_config_tready => s_axis_config_tready, s_axis_data_tdata => s_axis_data_tdata, s_axis_data_tvalid => s_axis_data_tvalid, s_axis_data_tready => s_axis_data_tready, s_axis_data_tlast => s_axis_data_tlast, m_axis_data_tdata => m_axis_data_tdata, m_axis_data_tvalid => m_axis_data_tvalid, m_axis_data_tready => m_axis_data_tready, m_axis_data_tlast => m_axis_data_tlast, event_frame_started => event_frame_started, event_tlast_unexpected => event_tlast_unexpected, event_tlast_missing => event_tlast_missing, event_status_channel_halt => event_status_channel_halt, event_data_in_channel_halt => event_data_in_channel_halt, event_data_out_channel_halt => event_data_out_channel_halt ); -- INST_TAG_END ------ End INSTANTIATION Template ------------ end Behavioral; Podczas generacji modułów "IP Core FFT V.8" został także utworzony test-bench, który zamierzam wykorzystać do pierwszych testów FFT - oto jego kod: --------------------------------------------------------------------------- -- -- (c) Copyright 2010 Xilinx, Inc. All rights reserved. -- -- This file contains confidential and proprietary information -- of Xilinx, Inc. and is protected under U.S. and -- international copyright and other intellectual property -- laws. -- -- DISCLAIMER -- This disclaimer is not a license and does not grant any -- rights to the materials distributed herewith. Except as -- otherwise provided in a valid license issued to you by -- Xilinx, and to the maximum extent permitted by applicable -- law: (1) THESE MATERIALS ARE MADE AVAILABLE "AS IS" AND -- WITH ALL FAULTS, AND XILINX HEREBY DISCLAIMS ALL WARRANTIES -- AND CONDITIONS, EXPRESS, IMPLIED, OR STATUTORY, INCLUDING -- BUT NOT LIMITED TO WARRANTIES OF MERCHANTABILITY, NON- -- INFRINGEMENT, OR FITNESS FOR ANY PARTICULAR PURPOSE; and -- (2) Xilinx shall not be liable (whether in contract or tort, -- including negligence, or under any other theory of -- liability) for any loss or damage of any kind or nature -- related to, arising under or in connection with these -- materials, including for any direct, or any indirect, -- special, incidental, or consequential loss or damage -- (including loss of data, profits, goodwill, or any type of -- loss or damage suffered as a result of any action brought -- by a third party) even if such damage or loss was -- reasonably foreseeable or Xilinx had been advised of the -- possibility of the same. -- -- CRITICAL APPLICATIONS -- Xilinx products are not designed or intended to be fail- -- safe, or for use in any application requiring fail-safe -- performance, such as life-support or safety devices or -- systems, Class III medical devices, nuclear facilities, -- applications related to the deployment of airbags, or any -- other applications that could lead to death, personal -- injury, or severe property or environmental damage -- (individually and collectively, "Critical -- Applications"). Customer assumes the sole risk and -- liability of any use of Xilinx products in Critical -- Applications, subject only to applicable laws and -- regulations governing limitations on product liability. -- -- THIS COPYRIGHT NOTICE AND DISCLAIMER MUST BE RETAINED AS -- PART OF THIS FILE AT ALL TIMES. -- --------------------------------------------------------------------------- -- Description: -- This is an example testbench for the Fast Fourier Transform (FFT) LogiCORE module. -- The testbench has been generated by the Xilinx CORE Generator software -- to accompany the netlist you have generated. -- -- This testbench is for demonstration purposes only. See note below for -- instructions on how to use it with the netlist created for your core. -- -- See the FFT datasheet for further information about this core. -- --------------------------------------------------------------------------- -- Using this testbench -- -- This testbench instantiates your generated FFT core named "FFT_IP8". -- -- If your CORE Generator project options were set to generate a structural -- model, a VHDL netlist named FFT_IP8.vhd was generated. -- If this file is not present, execute the following command in the directory -- containing your CORE Generator output files, to create a VHDL netlist: -- -- netgen -sim -ofmt vhdl FFT_IP8.ngc FFT_IP8.vhd -- -- Compile FFT_IP8.vhd into the work library. See your simulator -- documentation for more information on how to do this. -- --------------------------------------------------------------------------- library ieee; use ieee.std_logic_1164.all; use ieee.numeric_std.all; use ieee.math_real.all; entity tb_FFT_IP8 is end tb_FFT_IP8; architecture tb of tb_FFT_IP8 is ----------------------------------------------------------------------- -- Timing constants ----------------------------------------------------------------------- constant CLOCK_PERIOD : time := 100 ns; constant T_HOLD : time := 10 ns; constant T_STROBE : time := CLOCK_PERIOD - (1 ns); ----------------------------------------------------------------------- -- DUT signals ----------------------------------------------------------------------- -- General signals signal aclk : std_logic := '0'; -- the master clock -- Config slave channel signals signal s_axis_config_tvalid : std_logic := '0'; -- payload is valid signal s_axis_config_tready : std_logic := '1'; -- slave is ready signal s_axis_config_tdata : std_logic_vector(15 downto 0) := (others => '0'); -- data payload -- Data slave channel signals signal s_axis_data_tvalid : std_logic := '0'; -- payload is valid signal s_axis_data_tready : std_logic := '1'; -- slave is ready signal s_axis_data_tdata : std_logic_vector(31 downto 0) := (others => '0'); -- data payload signal s_axis_data_tlast : std_logic := '0'; -- indicates end of packet -- Data master channel signals signal m_axis_data_tvalid : std_logic := '0'; -- payload is valid signal m_axis_data_tready : std_logic := '1'; -- slave is ready signal m_axis_data_tdata : std_logic_vector(31 downto 0) := (others => '0'); -- data payload signal m_axis_data_tlast : std_logic := '0'; -- indicates end of packet -- Event signals signal event_frame_started : std_logic := '0'; signal event_tlast_unexpected : std_logic := '0'; signal event_tlast_missing : std_logic := '0'; signal event_status_channel_halt : std_logic := '0'; signal event_data_in_channel_halt : std_logic := '0'; signal event_data_out_channel_halt : std_logic := '0'; ----------------------------------------------------------------------- -- Aliases for AXI channel TDATA and TUSER fields -- These are a convenience for viewing data in a simulator waveform viewer. -- If using ModelSim or Questa, add "-voptargs=+acc=n" to the vsim command -- to prevent the simulator optimizing away these signals. ----------------------------------------------------------------------- -- Config slave channel alias signals signal s_axis_config_tdata_fwd_inv : std_logic := '0'; -- forward or inverse signal s_axis_config_tdata_scale_sch : std_logic_vector(9 downto 0) := (others => '0'); -- scaling schedule -- Data slave channel alias signals signal s_axis_data_tdata_re : std_logic_vector(15 downto 0) := (others => '0'); -- real data signal s_axis_data_tdata_im : std_logic_vector(15 downto 0) := (others => '0'); -- imaginary data -- Data master channel alias signals signal m_axis_data_tdata_re : std_logic_vector(15 downto 0) := (others => '0'); -- real data signal m_axis_data_tdata_im : std_logic_vector(15 downto 0) := (others => '0'); -- imaginary data ----------------------------------------------------------------------- -- Constants, types and functions to create input data ----------------------------------------------------------------------- constant IP_WIDTH : integer := 16; constant MAX_SAMPLES : integer := 2**10; -- maximum number of samples in a frame type T_IP_SAMPLE is record re : std_logic_vector(IP_WIDTH-1 downto 0); im : std_logic_vector(IP_WIDTH-1 downto 0); end record; type T_IP_TABLE is array (0 to MAX_SAMPLES-1) of T_IP_SAMPLE; -- Zeroed input data table, for reset and initialization constant IP_TABLE_CLEAR : T_IP_TABLE := (others => (re => (others => '0'), im => (others => '0'))); -- Function to generate input data table -- Data is a complex sinusoid exp(-jwt) with a frequency 2.6 times the frame size -- added to another with a lower magnitude and a higher frequency function create_ip_table return T_IP_TABLE is variable result : T_IP_TABLE; variable theta : real; variable theta2 : real; variable re_real : real; variable im_real : real; variable re_int : integer; variable im_int : integer; begin for i in 0 to MAX_SAMPLES-1 loop theta := real(i) / real(MAX_SAMPLES) * 2.6 * 2.0 * MATH_PI; re_real := cos(-theta); im_real := sin(-theta); theta2 := real(i) / real(MAX_SAMPLES) * 23.2 * 2.0 * MATH_PI; re_real := re_real + (cos(-theta2) / 4.0); im_real := im_real + (sin(-theta2) / 4.0); re_int := integer(round(re_real * real(2**(IP_WIDTH-2)))); im_int := integer(round(im_real * real(2**(IP_WIDTH-2)))); result(i).re := std_logic_vector(to_signed(re_int, IP_WIDTH)); result(i).im := std_logic_vector(to_signed(im_int, IP_WIDTH)); end loop; return result; end function create_ip_table; -- Call the function to create the input data constant IP_DATA : T_IP_TABLE := create_ip_table; ----------------------------------------------------------------------- -- Testbench signals ----------------------------------------------------------------------- -- Communication between processes regarding DUT configuration type T_DO_CONFIG is (NONE, IMMEDIATE, AFTER_START, DONE); shared variable do_config : T_DO_CONFIG := NONE; -- instruction for driving config slave channel type T_CFG_FWD_INV is (FWD, INV); signal cfg_fwd_inv : T_CFG_FWD_INV := FWD; type T_CFG_SCALE_SCH is (ZERO, DEFAULT); signal cfg_scale_sch : T_CFG_SCALE_SCH := DEFAULT; -- Recording output data, for reuse as input data signal op_sample : integer := 0; -- output sample number signal op_sample_first : std_logic := '1'; -- indicates first output sample of a frame signal ip_frame : integer := 0; -- input / configuration frame number signal op_data : T_IP_TABLE := IP_TABLE_CLEAR; -- recorded output data signal op_frame : integer := 0; -- output frame number (incremented at end of frame output) begin ----------------------------------------------------------------------- -- Instantiate the DUT ----------------------------------------------------------------------- dut : entity work.FFT_IP8 port map ( aclk => aclk, s_axis_config_tvalid => s_axis_config_tvalid, s_axis_config_tready => s_axis_config_tready, s_axis_config_tdata => s_axis_config_tdata, s_axis_data_tvalid => s_axis_data_tvalid, s_axis_data_tready => s_axis_data_tready, s_axis_data_tdata => s_axis_data_tdata, s_axis_data_tlast => s_axis_data_tlast, m_axis_data_tvalid => m_axis_data_tvalid, m_axis_data_tready => m_axis_data_tready, m_axis_data_tdata => m_axis_data_tdata, m_axis_data_tlast => m_axis_data_tlast, event_frame_started => event_frame_started, event_tlast_unexpected => event_tlast_unexpected, event_tlast_missing => event_tlast_missing, event_status_channel_halt => event_status_channel_halt, event_data_in_channel_halt => event_data_in_channel_halt, event_data_out_channel_halt => event_data_out_channel_halt ); ----------------------------------------------------------------------- -- Generate clock ----------------------------------------------------------------------- clock_gen : process begin aclk <= '0'; wait for CLOCK_PERIOD; loop aclk <= '0'; wait for CLOCK_PERIOD/2; aclk <= '1'; wait for CLOCK_PERIOD/2; end loop; end process clock_gen; ----------------------------------------------------------------------- -- Generate data slave channel inputs ----------------------------------------------------------------------- data_stimuli : process -- Variables for random number generation variable seed1, seed2 : positive; variable rand : real; -- Procedure to drive an input sample with specific data -- data is the data value to drive on the tdata signal -- last is the bit value to drive on the tlast signal -- valid_mode defines how to drive TVALID: 0 = TVALID always high, 1 = TVALID low occasionally procedure drive_sample ( data : std_logic_vector(31 downto 0); last : std_logic; valid_mode : integer := 0 ) is begin s_axis_data_tdata <= data; s_axis_data_tlast <= last; if valid_mode = 1 then uniform(seed1, seed2, rand); -- generate random number if rand < 0.25 then s_axis_data_tvalid <= '0'; uniform(seed1, seed2, rand); -- generate another random number wait for CLOCK_PERIOD * integer(round(rand * 4.0)); -- hold TVALID low for up to 4 cycles s_axis_data_tvalid <= '1'; -- now assert TVALID else s_axis_data_tvalid <= '1'; end if; else s_axis_data_tvalid <= '1'; end if; loop wait until rising_edge(aclk); exit when s_axis_data_tready = '1'; end loop; wait for T_HOLD; s_axis_data_tvalid <= '0'; end procedure drive_sample; -- Procedure to drive an input frame with a table of data -- data is the data table containing input data -- valid_mode defines how to drive TVALID: 0 = TVALID always high, 1 = TVALID low occasionally procedure drive_frame ( data : T_IP_TABLE; valid_mode : integer := 0 ) is variable samples : integer; variable index : integer; variable sample_data : std_logic_vector(31 downto 0); variable sample_last : std_logic; begin samples := data'length; index := 0; while index < data'length loop -- Look up sample data in data table, construct TDATA value sample_data(15 downto 0) := data(index).re; -- real data sample_data(31 downto 16) := data(index).im; -- imaginary data -- Construct TLAST's value index := index + 1; if index >= data'length then sample_last := '1'; else sample_last := '0'; end if; -- Drive the sample drive_sample(sample_data, sample_last, valid_mode); end loop; end procedure drive_frame; variable op_data_saved : T_IP_TABLE; -- to save a copy of recorded output data begin -- Drive inputs T_HOLD time after rising edge of clock wait until rising_edge(aclk); wait for T_HOLD; -- Drive a frame of input data ip_frame <= 1; drive_frame(IP_DATA); -- Allow the result to emerge wait until m_axis_data_tlast = '1'; wait until rising_edge(aclk); wait for T_HOLD; -- Take a copy of the result, to use later as input op_data_saved := op_data; -- Now perform an inverse transform on the result to get back to the original input -- Set up the configuration (config_stimuli process handles the config slave channel) ip_frame <= 2; cfg_fwd_inv <= INV; do_config := IMMEDIATE; while do_config /= DONE loop wait until rising_edge(aclk); end loop; wait for T_HOLD; -- Configuration is done. Set up another configuration to return to forward transforms, -- and make the configuration occur as soon as the next frame has begun ip_frame <= 3; cfg_fwd_inv <= FWD; do_config := AFTER_START; -- Now drive the input data, using the output data of the last frame drive_frame(op_data); wait until m_axis_data_tlast = '1'; wait until rising_edge(aclk); wait for T_HOLD; -- The frame is complete, and the configuration to forward transforms has already been done, -- so drive the input data, using the output data of the last frame, -- which is the same as the original input (excepting scaling and finite precision effects). -- This time, deassert the data slave channel TVALID occasionally to illustrate AXI handshaking effects: -- as the core is configured to use Non Real Time throttle scheme, it will pause when TVALID is low. drive_frame(op_data, 1); -- During the output of this frame, deassert the data master channel TREADY occasionally: -- as the core is configured to use Non Real Time throttle scheme, it will pause when TREADY is low. wait until m_axis_data_tvalid = '1'; wait until rising_edge(aclk); while m_axis_data_tlast /= '1' loop wait for T_HOLD; uniform(seed1, seed2, rand); -- generate random number if rand < 0.25 then m_axis_data_tready <= '0'; else m_axis_data_tready <= '1'; end if; wait until rising_edge(aclk); end loop; wait for T_HOLD; m_axis_data_tready <= '1'; wait for CLOCK_PERIOD; -- Now run 4 back-to-back transforms, as quickly as possible. -- First queue up 2 configurations: these will be applied successively over the next 2 transforms. -- 1st configuration ip_frame <= 4; cfg_fwd_inv <= FWD; -- forward transform cfg_scale_sch <= DEFAULT; -- default scaling schedule do_config := IMMEDIATE; while do_config /= DONE loop wait until rising_edge(aclk); end loop; wait for T_HOLD; -- 2nd configuration: same as 1st, except: ip_frame <= 5; cfg_fwd_inv <= INV; -- inverse transform cfg_scale_sch <= ZERO; -- no scaling do_config := IMMEDIATE; while do_config /= DONE loop wait until rising_edge(aclk); end loop; wait for T_HOLD; -- Drive the 1st data frame drive_frame(IP_DATA); -- Request a 3rd configuration, to be sent after 2nd data frame starts ip_frame <= 6; cfg_fwd_inv <= FWD; -- forward transform cfg_scale_sch <= ZERO; -- no scaling do_config := AFTER_START; -- Drive the 2nd data frame drive_frame(op_data_saved); -- Request a 4th configuration, to be sent after 3rd data frame starts: same as 3rd, except: ip_frame <= 7; cfg_fwd_inv <= INV; -- inverse transform cfg_scale_sch <= DEFAULT; -- default scaling schedule do_config := AFTER_START; -- Drive the 3rd data frame drive_frame(IP_DATA); -- Drive the 4th data frame drive_frame(op_data_saved); -- Wait until all the output data from all frames has been produced wait until op_frame = 7; wait for CLOCK_PERIOD * 10; -- End of test report "Not a real failure. Simulation finished successfully." severity failure; wait; end process data_stimuli; ----------------------------------------------------------------------- -- Generate config slave channel inputs ----------------------------------------------------------------------- config_stimuli : process variable scale_sch : std_logic_vector(9 downto 0); begin -- Drive a configuration when requested by data_stimuli process wait until rising_edge(aclk); while do_config = NONE or do_config = DONE loop wait until rising_edge(aclk); end loop; -- If the configuration is requested to occur after the next frame starts, wait for that event if do_config = AFTER_START then wait until event_frame_started = '1'; wait until rising_edge(aclk); end if; -- Drive inputs T_HOLD time after rising edge of clock wait for T_HOLD; -- Construct the config slave channel TDATA signal s_axis_config_tdata <= (others => '0'); -- clear unused bits -- Format the transform direction if cfg_fwd_inv = FWD then s_axis_config_tdata(0) <= '1'; -- forward elsif cfg_fwd_inv = INV then s_axis_config_tdata(0) <= '0'; -- inverse end if; -- Format the scaling schedule if cfg_scale_sch = ZERO then -- no scaling scale_sch := (others => '0'); elsif cfg_scale_sch = DEFAULT then -- default scaling, for largest magnitude output with no overflow guaranteed scale_sch(1 downto 0) := "11"; -- largest scaling at first stage for s in 2 to 5 loop scale_sch(s*2-1 downto s*2-2) := "10"; -- less scaling at later stages end loop; end if; s_axis_config_tdata(10 downto 1) <= scale_sch; -- Drive the transaction on the config slave channel s_axis_config_tvalid <= '1'; loop wait until rising_edge(aclk); exit when s_axis_config_tready = '1'; end loop; wait for T_HOLD; s_axis_config_tvalid <= '0'; -- Tell the data_stimuli process that the configuration has been done do_config := DONE; end process config_stimuli; ----------------------------------------------------------------------- -- Record outputs, to use later as inputs for another frame ----------------------------------------------------------------------- record_outputs : process (aclk) -- Function to digit-reverse an integer, to convert output to input ordering function digit_reverse_int ( fwd, width : integer ) return integer is variable rev : integer; variable fwd_slv : std_logic_vector(width-1 downto 0); variable rev_slv : std_logic_vector(width-1 downto 0); begin fwd_slv := std_logic_vector(to_unsigned(fwd, width)); for i in 0 to width/2-1 loop -- reverse in digit groups (2 bits at a time) rev_slv(i*2+1 downto i*2) := fwd_slv(width-i*2-1 downto width-i*2-2); end loop; if width mod 2 = 1 then -- width is odd: LSB moves to MSB rev_slv(width-1) := fwd_slv(0); end if; rev := to_integer(unsigned(rev_slv)); return rev; end function digit_reverse_int; variable index : integer := 0; begin if rising_edge(aclk) then if m_axis_data_tvalid = '1' and m_axis_data_tready = '1' then -- Record output data such that it can be used as input data index := op_sample; -- Digit-reverse output sample number, to get actual sample index as outputs are in digit-reversed order index := digit_reverse_int(index, 10); op_data(index).re <= m_axis_data_tdata(15 downto 0); op_data(index).im <= m_axis_data_tdata(31 downto 16); -- Increment output sample counter if m_axis_data_tlast = '1' then -- end of output frame: reset sample counter and increment frame counter op_sample <= 0; op_frame <= op_frame + 1; op_sample_first <= '1'; -- for next output frame else op_sample_first <= '0'; op_sample <= op_sample + 1; end if; end if; end if; end process record_outputs; ----------------------------------------------------------------------- -- Check outputs ----------------------------------------------------------------------- check_outputs : process variable check_ok : boolean := true; -- Previous values of data master channel signals variable m_data_tvalid_prev : std_logic := '0'; variable m_data_tready_prev : std_logic := '0'; variable m_data_tdata_prev : std_logic_vector(31 downto 0) := (others => '0'); begin -- Check outputs T_STROBE time after rising edge of clock wait until rising_edge(aclk); wait for T_STROBE; -- Do not check the output payload values, as this requires a numerical model -- which would make this demonstration testbench unwieldy. -- Instead, check the protocol of the data master channel: -- check that the payload is valid (not X) when TVALID is high -- and check that the payload does not change while TVALID is high until TREADY goes high if m_axis_data_tvalid = '1' then if is_x(m_axis_data_tdata) then report "ERROR: m_axis_data_tdata is invalid when m_axis_data_tvalid is high" severity error; check_ok := false; end if; if m_data_tvalid_prev = '1' and m_data_tready_prev = '0' then -- payload must be the same as last cycle if m_axis_data_tdata /= m_data_tdata_prev then report "ERROR: m_axis_data_tdata changed while m_axis_data_tvalid was high and m_axis_data_tready was low" severity error; check_ok := false; end if; end if; end if; assert check_ok report "ERROR: terminating test with failures." severity failure; -- Record payload values for checking next clock cycle if check_ok then m_data_tvalid_prev := m_axis_data_tvalid; m_data_tready_prev := m_axis_data_tready; m_data_tdata_prev := m_axis_data_tdata; end if; end process check_outputs; ----------------------------------------------------------------------- -- Assign TDATA / TUSER fields to aliases, for easy simulator waveform viewing ----------------------------------------------------------------------- -- Config slave channel alias signals s_axis_config_tdata_fwd_inv <= s_axis_config_tdata(0); s_axis_config_tdata_scale_sch <= s_axis_config_tdata(10 downto 1); -- Data slave channel alias signals s_axis_data_tdata_re <= s_axis_data_tdata(15 downto 0); s_axis_data_tdata_im <= s_axis_data_tdata(31 downto 16); -- Data master channel alias signals m_axis_data_tdata_re <= m_axis_data_tdata(15 downto 0); m_axis_data_tdata_im <= m_axis_data_tdata(31 downto 16); end tb; A tutaj spakowany kod projektu dla "ISE 14.7 Webpack": FFT_IPCore8_01.zip Zachęcam do własnych prób z tym projektem. Ciąg dalszy nastąpi ... Pozdrawiam

-

Gra "Snake" na płytce FPGA "Mimas v.2" (Spartan6)

FlyingDutch opublikował temat w Układy programowalne

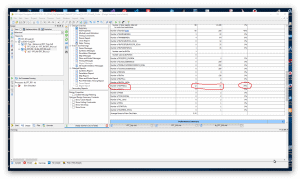

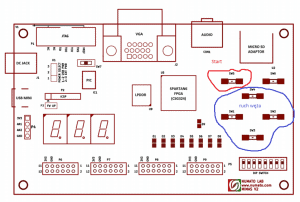

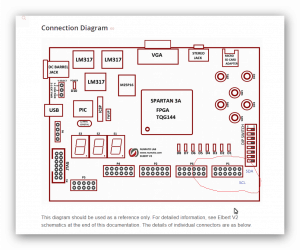

Cześć, ponieważ w ciągu tego roku byłem tak obciążony projektami elektronicznymi w pracy (i ich programowaniem), że nie mam w czasie wolnym ochoty na ambitne projekty. Ponieważ mam teraz kilka dni wolnych postanowiłem zająć się jakimś małym projektem, który da mi trochę rozrywki. Jak już kiedyś pisałem w latach 80-tych lubiłem grać w proste gry na "automatach", dlatego wybór padł znów na prostą grę "Snake"(wąż). Wybór padł na implementację tej gry na płytkę FPGA "Pepino" (także Spartan6) - niestety różni się sporo od Mimas V.2. Tutaj link do żródeł gry na Githgub'ie: https://github.com/Saanlima/Pepino/tree/master/Projects/Snake Przystępując do implementacji gry myślałem, że powinno udać się ją uruchomić na zestawie FPGA "Elbert V.2" (Spartan3) - niestety okazało się, iż liczba wymaganych zasobów jest ponad dwukrotnie większa od tej którą posiada ta płytka. Gra wymaga 1957 przerzutników (FF) i 1703 LUTs - patrz zrzut erranu z ISE: Tak, że mój wybór padł na zestaw FPGA "Mimas V.2", który posiadam od kilku lat. Tutaj linki do tego zestawu w Botland'zie oraz do producenta firmy "Numato Labs": https://botland.com.pl/moduly-i-zestawy-fpga/8603-mimas-v2-spartan-6-plytka-rozwojowa-fpga-5904422311964.html https://numato.com/product/mimas-v2-spartan-6-fpga-development-board-with-ddr-sdram/ https://numato.com/docs/mimas-v2-spartan-6-fpga-development-board-with-ddr-sdram/ Podstawową różnicą pomiędzy oryginalnym projektem na zestaw FPGA "Pepino" jest fakt, iż "Pepino" ma główny zegar 50 Mhz a Mimas v.2 100 Mhz. Poza tym ruch węża był realizowany poprzez klawiaturę PS2 podłączoną do plytki FPGA - ponieważ nie posiadam takiej klawiatury postanowiłem kontrolować ruch węża za pomocą przycisków na płytce Mimas. Z tego powodu można było usunąć dwa sygnały wejściowe: KB_clk i KB_data z głównego modułu aplikacji(Snake.v), i sam moduł obsługi klawiatury: kbInput(VGA_clk, KB_clk, KB_data, direction) Trzeba też było zmodyfikować plik "user constraints" (ucf) tak aby pasował do zestawu FPGA 'Mimas v.2". Oto lista wykonanych w projekcie zmian: 1) Zmodyfikowanie portów głównego modułu Snake.v: było: module Snake(start, master_clk, KB_clk, KB_data, VGA_R, VGA_G, VGA_B, VGA_hSync, VGA_vSync); input start; input master_clk, KB_clk, KB_data; output reg [2:0] VGA_R; output reg [2:0] VGA_G; output reg [1:0] VGA_B; output VGA_hSync, VGA_vSync; po modyfikacji: module Snake(start, clk100, VGA_R, VGA_G, VGA_B, VGA_hSync, VGA_vSync, btnUp, btnDown, btnLeft, btnRight); input start; input clk100; input btnUp, btnDown, btnLeft, btnRight; output reg [2:0] VGA_R; output reg [2:0] VGA_G; output reg [1:0] VGA_B; output VGA_hSync, VGA_vSync; 2) Usunięto moduł zegarowy w głównym module: // Use a CDM to generate VGA clock (25 MHz) from input clock (50 MHz) DCM #(.CLKIN_DIVIDE_BY_2("TRUE"), .CLKIN_PERIOD(20.000)) dcm(.CLKIN(master_clk), .CLKFB(VGA_clk), .RST(1'b0), .PSEN(1'b0), .PSINCDEC(1'b0), .PSCLK(1'b0), .DSSEN(1'b0), .CLK0(VGA_clk)); a dodano DCM (IPCore PLL_Clock), który teraz z zegara Mimas'a 100 MHz generuje dwa zegary (50 Mhz i 25 Mhz do taktowania modułu VGA): // Instantiate the module PLL_Clock PLL1 (// Clock in ports .CLK_IN1(clk100), // IN 100Mhz // Clock out ports .CLK_OUT1(master_clk), // OUT 50Mhz .CLK_OUT2(VGA_clk)); // OUT 25MHz 3) Usunięte zostało wywołanie modułu: kbInput i kod samego modułu: VGA_gen gen1(VGA_clk, xCount, yCount, displayArea, VGA_hSync, VGA_vSync); randomGrid rand1(VGA_clk, rand_X, rand_Y); //kbInput kbIn(VGA_clk, KB_clk, KB_data, direction); updateClk UPDATE(VGA_clk, update); module kbInput(VGA_clk, KB_clk, KB_data, direction); input VGA_clk; input KB_clk; input KB_data; output reg [3:0] direction = 4'b0000; reg Q0, Q1; reg [10:0] shreg; reg [7:0] code; wire endbit; assign endbit = ~shreg[0]; assign shift = Q1 & ~Q0; always @ (posedge VGA_clk) begin Q0 <= KB_clk; Q1 <= Q0; shreg <= (endbit) ? 11'h7FF : shift ? {KB_data, shreg[10:1]} : shreg; if (endbit) code <= shreg[8:1]; if(code == 8'h1D) direction <= 4'b0001; else if(code == 8'h1C) direction <= 4'b0010; else if(code == 8'h1B) direction <= 4'b0100; else if(code == 8'h23) direction <= 4'b1000; end endmodule zamiast tego został dodany fragment kodu obsługujący przyciski z płytki Mimas w module głównym (linie od 79 do 87): end else if (~game_over) begin if (update) begin for(count = 1; count < 128; count = count + 1) begin if(size > count) begin snakeX[count] <= snakeX[count - 1]; snakeY[count] <= snakeY[count - 1]; end end //obsluga przycisow z Mimasa if(btnDown == 1'b0) direction <= 4'b0001; else if(btnLeft == 1'b0) direction <= 4'b0010; else if(btnUp == 1'b0) direction <= 4'b0100; else if(btnRight == 1'b0) direction <= 4'b1000; case(direction) 4'b0001: snakeY[0] <= (snakeY[0] - 1); 4'b0010: snakeX[0] <= (snakeX[0] - 1); 4'b0100: snakeY[0] <= (snakeY[0] + 1); 4'b1000: snakeX[0] <= (snakeX[0] + 1); endcase Poniżej rysunek z przyciskami z Mimas'a użytymi do kontrolowania ruchu węża i gry: Przycisk SW5 to start nowej gry a przyciski:SW!, SW2, SW3, SW4 kontrolują ruch węża. Poniżej zdjęcie z gry uruchomionej na zestawie Mimas v.2 i małym monitorku VGA: Bym zapomniał: był jeszcze błąd języka Verilog w tym fragmencie kodu: module randomGrid(VGA_clk, rand_X, rand_Y); input VGA_clk; output reg [6:0] rand_X; output reg [6:0] rand_Y; always @(posedge VGA_clk) begin //rand_X <= ((rand_X + 3) % 78) + 1; //rand_Y <= ((rand_Y + 5) % 58) + 1; rand_X <= ((rand_X + 3) % 64) + 1; rand_Y <= ((rand_Y + 5) % 32) + 1; end endmodule dwie linie zostały wykomentowane i dodane dwie poniżej (zmienione) - Verilog wymaga, aby drugi argument operatora modulo % był potęgą liczby dwa. Tutaj plik "Snake.ucf" (z user constraints) dla płytki Mimas v.2: NET "*" IOSTANDARD=LVCMOS33; CONFIG VCCAUX = "3.3" ; # Clock 100 MHz NET "clk100" LOC = V10 | IOSTANDARD = LVCMOS33 | PERIOD = 100MHz ; NET "start" LOC = K17 | PULLUP; #SW5 # VGA port NET "VGA_hSync" LOC = B12; NET "VGA_vSync" LOC = A12; NET "VGA_R<0>" LOC = A9; NET "VGA_R<1>" LOC = B9; NET "VGA_R<2>" LOC = C9; NET "VGA_G<0>" LOC = C10; NET "VGA_G<1>" LOC = A10; NET "VGA_G<2>" LOC = C11; NET "VGA_B<0>" LOC = B11; NET "VGA_B<1>" LOC = A11; # Przyciski Mimas V.2 NET "btnLeft" LOC = M18 | IOSTANDARD = LVCMOS33 | DRIVE = 8 | SLEW = FAST | PULLUP; #SW1 NET "btnRight" LOC = L18 | IOSTANDARD = LVCMOS33 | DRIVE = 8 | SLEW = FAST | PULLUP; #SW2 NET "btnDown" LOC = L17 | IOSTANDARD = LVCMOS33 | DRIVE = 8 | SLEW = FAST | PULLUP; #SW3 NET "btnUp" LOC = M16 | IOSTANDARD = LVCMOS33 | DRIVE = 8 | SLEW = FAST | PULLUP; #SW4 Zamieszczam spakowany projekt gry dla "ISE 14.7 Webpack": SnakeGame.zip Plik binarny do wgrania konfiguracji FPGA to "snake.bin" (jeśli ktoś nie jest zainteresowany kodem źródłowym). Pozdrawiam -