Całościowy bardziej zaawansowany kurs VHDL (j. angielski)

-

Quizy

-

Najnowsze posty w innych tematach

-

Kurs Arduino - #7 - Wyświetlacz tekstowy, LCD 2x16 1 2 3 4 28

Przez Komentator, w Artykuły redakcji (blog)

- 410 odp.

- 109 592 wyświetleń

-

- 10 odp.

- 438 wyświetleń

-

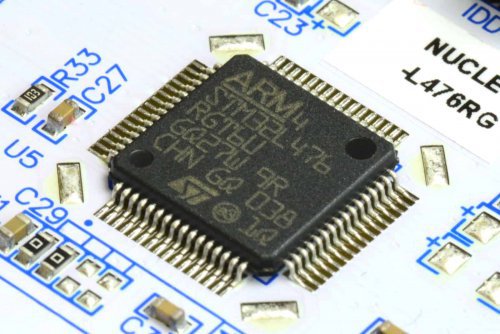

Komunikacja bezprzewodowa Arduino UNO z Nucleo L476RG przy pomocy NRF24L01

Przez Blasteee123, w Arduino i ESP

- 2 odp.

- 47 wyświetleń

-

- 3 odp.

- 150 wyświetleń

-

Problemy ze środowiskiem ISE Xilinx w Windows 10

Przez pszajow, w Układy programowalne

- Xilinx

- Windows 10

- (i 2 więcej)

- 5 odp.

- 2 137 wyświetleń

-

Pomocna odpowiedź

Dołącz do dyskusji, napisz odpowiedź!

Jeśli masz już konto to zaloguj się teraz, aby opublikować wiadomość jako Ty. Możesz też napisać teraz i zarejestrować się później.

Uwaga: wgrywanie zdjęć i załączników dostępne jest po zalogowaniu!