Kursy • Poradniki • Inspirujące DIY • Forum

Czym jest automat skończony?

Automaty skończone stanowią punkt wyjścia dla modelowania układów cyfrowych oraz szeroko pojętych systemów informatycznych. Zasada działania mechanizmów tego typu przydaje się nie tylko podczas pisania programów w VHDL. Podobne algorytmy są spotykane również w programach, zarówno tych na komputery PC, jak i na mikrokontrolery, czyli np. Arduino.

Automat stanów oraz maszyna stanów

to nazewnictwo używane zamiennie.

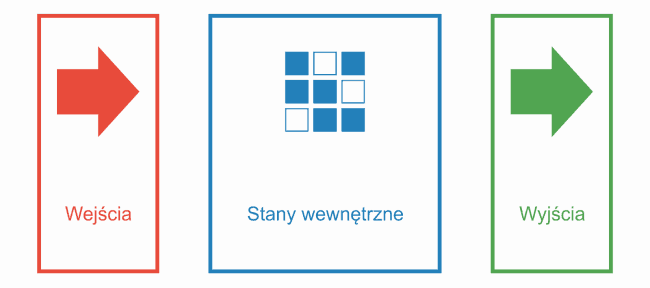

Na początek wprowadzimy pojęcia odnoszące się do typów układów cyfrowych:

- Układy Kombinacyjne - to układy, w których zmiany wejść dają bezpośrednią i prawie natychmiastową reakcje na wyjściach systemu. Przykładem układu kombinacyjnego jest układ złożony jedynie z bramek logicznych lub multiplekser.

- Układy Sekwencyjne - to układy posiadające stany wewnętrzne (pamięć), więc wyjścia zależą od wejść oraz od stanów wewnętrznych. Przykładem może być układ licznika oraz rejestr przesuwny.

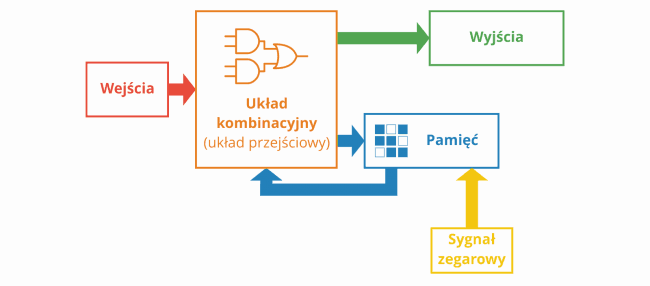

W przypadku układów sekwencyjnych wyróżnia się dwa rodzaje:

- Układy synchroniczne - każdy element pamięciowy (przerzutnik) jest sterowany wspólnym sygnałem zegarowym. Dzięki temu wszystkie przerzutniki są przełączane równocześnie i cały układ przechodzi równocześnie z jednego stanu do drugiego.

- Układy asynchroniczne - zależnie od konstrukcji, jedne przerzutniki mogą być sterowane poprzez wyjścia innych przerzutników. Układy te są najbardziej skomplikowane i mogą na początku sprawiać pewne problemy.

W tym artykule skupimy się na układach synchronicznych!

Aby zrozumieć automaty skończone musimy poznać pojęcie stanu. Stan jest to określona stabilna konfiguracja wewnętrzna systemu, która może być zmieniona pod wpływem zmiany wartości wejść systemu.

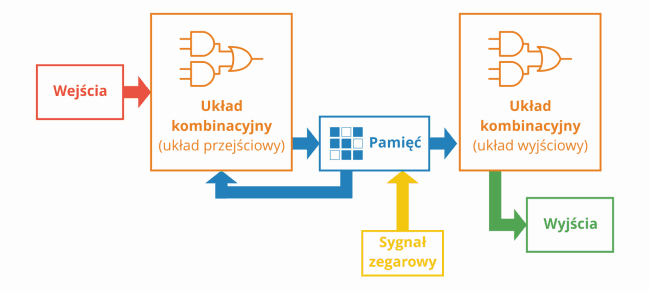

Ogólnie rzecz biorąc każdy system mikroprocesorowy bądź układ cyfrowy działa w oparciu o maszynę skończoną i składa się z następujących bloków:

- Blok wejść - za jego pomocą system otrzymuje informacje z zewnątrz. Prostym przykładem będzie informacja o wciśnięciu przycisku.

- Blok pamiętający stany wewnętrzne układu - systemy komputerowe przechowują te informacje w pamięci (np. typu Flash), w układach PLD rolę tę pełnią przerzutniki, które znajdują się w blokach logicznych.

- Blok wyjść - mogą to być diody świecące, sygnał VIDEO o określonych parametrach lub zupełnie inne sygnały, które mają być efektem działania układu.

Typy automatów skończonych

Wyróżnia się dwa najpopularniejsze typy automatów skończonych. Pierwszym z nich jest automat Mealy’ego. W tym układzie stany wyjść w danym momencie zależą od wejść układu oraz od jego aktualnych stanów wewnętrznych.

Drugim popularnym układem jest automat Moore'a. W jego przypadku wyjścia układu w danej chwili zależą wyłącznie od wewnętrznych stanów układu:

Funkcje automatów skończonych można opisać:

- tabelarycznie w postaci tabel prawdy,

- w formie grafu, który odwzorowuje działanie układu w sposób graficzny. Forma ta pozwala na łatwiejsze przedstawienie i zrozumienie działania układu.

Na ten moment nie będziemy zagłębiać się w teorię. Osoby zainteresowane szczegółami odsyłamy np. do Wikipedii: automat Mealy’ego, automat Moore’a.

Automaty stanów w praktyce

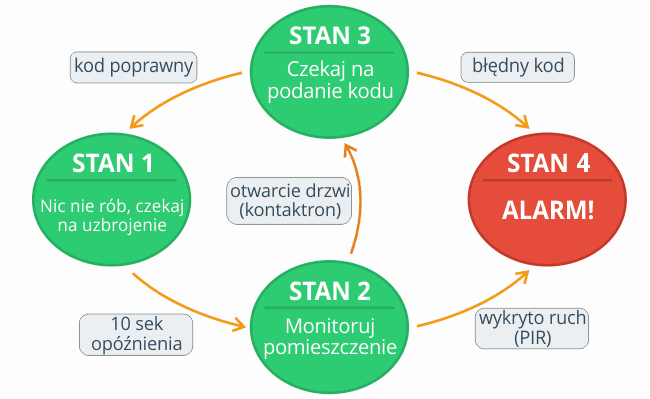

Opis ten może być dla niektórych początkujących zawiły. Więc przed przejściem do przykładu związanego z VHDL wrócimy na chwilę do kursu Arduino (poziom II). W jednym z jego odcinków opisywana była centralka alarmowa. Której działanie opierało się na 4 stanach:

- Czuwanie – alarm czeka na uzbrojenie.

- Monitorowanie – system pilnuje naszego pomieszczenia.

- Rozbrajanie – alarm czeka na wprowadzenie poprawnego pinu.

- Sygnalizacja alarmu – alarm wydaje dźwięki i sygnały świetlne.

Oczywiście funkcje te mogą następować po sobie tylko w odpowiedniej kolejności. Nie zdarzy się sytuacja, że będziemy rozbrajać alarm, gdy jest w czasie czuwania itd. Najlepiej widoczne jest to na poniższym schemacie (nie jest to graf stanów, traktujmy to jako prostą, graficzną reprezentację powyższych opisów):

Taka centralka alarmowa, to świetny przykład na urządzenie, które może pracować jako automat skończony. Realizacja tego projektu w "C" została opisana w 5. części kursu Arduino. Wróćmy jednak do VHDLa i zróbmy coś w praktyce!

Jak tworzyć automaty skończone?

Krok 1. Należy zdefiniować liczbę wejść, wyjść i stanów wewnętrznych układu.

Krok 2. Należy narysować graf, który będzie prezentował działanie automatu. Najłatwiej zacząć od narysowania stanów układu, a później dodać strzałki oznaczające przejścia między stanami.

Maszyna stanów w FPGA - przykład praktyczny

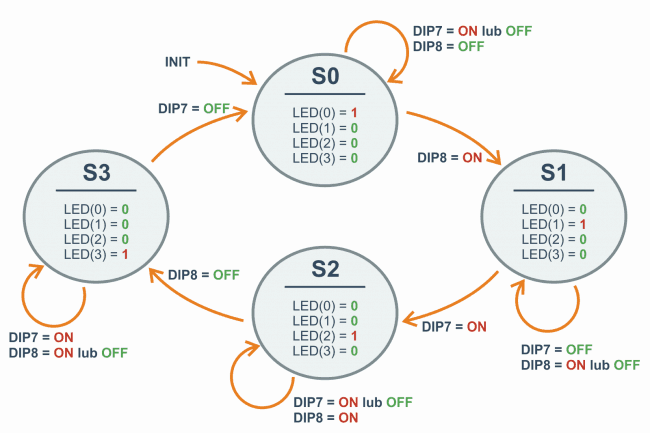

Oczywiście najlepiej zrozumieć omawiane zagadnienie w praktyce. Przykładowy projekt będzie korzystał z 4 diod świecących (D8, D7, D6, D5) oraz dwóch przełączników typu DIP-switch, które oznaczone są na zestawie jako nr 7 oraz 8.

Za pomocą wspomnianych dwóch przełączników będziemy mogli sterować przejściami układu między czterema stanami naszej maszyny stanów (będą one oczywiście wejściami). Informacje o aktualnym stanie odczytamy z diod świecących.

Działanie aplikacji opisuje poniższy graf - diagram maszyny stanów:

Wewnątrz "bąbelków" zostały umieszczone nazwy stanów (S0...S3) oraz wartości wyjść, gdy układ znajduje się w danym stanie (LED0...3). Przy strzałkach zaznaczono warunki tranzycji (przejść pomiędzy stanami). Zaznaczono również stan domyślny jako "init" - to właśnie w tym stanie układ znajdzie się automatycznie po włączeniu zasilania.

Jak czytać taki diagram?

Po włączeniu zasilania układ znajdzie się w stanie S0. Zaświeci się pierwsza z brzegu dioda. Układ przejdzie do stanu S1 tylko jeśli przełącznik DIP8 znajdzie się w stanie ON. Przy innych kombinacjach układ będzie ciągle pozostawał w S0.

Gdy powyższy warunek zostanie spełniony i znajdziemy się w stanie S1 to włączy się dioda, która będzie druga w kolejności. Układ pozostanie w tym stanie do momentu, w którym przełącznik DIP7 zostanie ustawiony w pozycję ON. Co ważne nie ma możliwości, aby układ cofnął się ze stanu S1 do S0! Pozostałe stany należy analizować analogicznie.

Gotowe zestawy do kursów Forbota

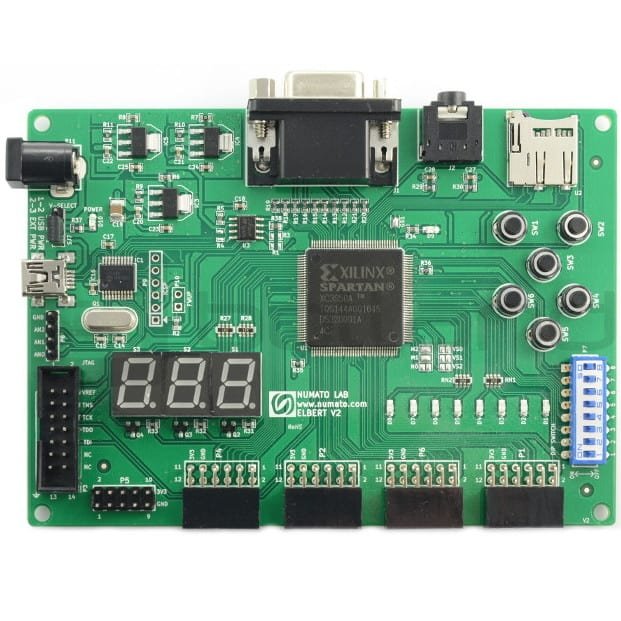

Komplet elementów Gwarancja pomocy Wysyłka w 24h

Zestaw uruchomieniowy Elbert v2 - Spartan 3A z wszystkimi niezbędnymi peryferiami do wykonania ćwiczeń z kursu FPGA!

Zamów w Botland.com.pl »Maszyna stanów w VHDL

Pora zrealizować układ w praktyce. W tym celu tworzymy nowy projekt. Standardowo zaczynamy od dodania bibliotek:

|

1 2 3 |

-- dodajemy biblioteki library IEEE; use IEEE.STD_LOGIC_1164.ALL; |

Następnie pora na blok enitity. Oprócz wspomnianych wcześniej przełączników DIP i LEDów będziemy korzystać z sygnału zegarowego Clk. Będzie on potrzebny w bloku process, wewnątrz którego będzie opisana funkcjonalność maszyny stanów.

|

1 2 3 4 5 |

entity maszyna_stanow is Port ( Clk : in STD_LOGIC; -- sygnal zegarowy jest uzywany w bloku process odpowiadajacym za dzialanie naszej maszyny stanow DPSwitch : in STD_LOGIC_VECTOR(1 downto 0); -- dwa przelaczniki DIP z ktorych korzystamy do poruszania sie pomiedzy stanami LED : out STD_LOGIC_VECTOR(3 downto 0)); -- 4 diody LED jako wyjscia end maszyna_stanow; |

W bloku architecture w obszarze deklarowania sygnałów lokalnych (czyli przed instrukcją begin) definiujemy nowy rodzaj sygnału. Typ ten może przyjąć wartości podane w nawiasie. Konstrukcja ta jest podobna do deklaracji zmiennej typu enum znanej z języka C. Mówiąc prościej, dzięki temu będziemy mogli tworzyć "zmienne", które będą przyjmowały tylko zdefiniowane przez nas wcześniej wartości (tutaj będą to nazwy kolejnych stanów):

|

1 2 3 |

-- ponizsza instrukcja definiuje nowy rodzaj sygnalu, ktory moze przyjac jedynie te wartosci -- ktore sa wymienione w nawiasie - konstrukcja ta jest podobna do definicji enum znanej z jezyka programowania C type typ_stanu is (S0, S1, S2, S3); -- Definiowanie stanow |

Niżej tworzymy sygnał wcześniej utworzonego typu. Sygnał ten nosi nazwę Stan. Będzie on przechowywał informacje na temat tego jaki stan panuje w naszym układzie. Przy okazji, od razu w tym miejscu została mu przypisana domyślna wartość S0 (nasz punkt startowy "Init").

|

1 |

signal Stan : typ_stanu := S0; -- Tworzenie sygnalu - zmiennej mogacej przyjmowac wartosci zdefiniowane w State_Type; |

Wewnątrz konstrukcji architecture (poniżej jej słowa kluczowego begin) opisujemy działanie układu. Gotowy kod prezentuje się następująco (został dokładnie omówiony poniżej):

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 |

process (Clk) begin if rising_edge(Clk) then -- gdy nastapi narastajace zbocze sygnalu zegarowego -- instrukcje zawarte ponizej beda wykonane -- Instrukcja CASE sprawdza wartosc sygnalu Stan, -- bazujac na jego wartosci jest wykonywany okreslony blok WHEN -- ktory jest wstanie zmienic wartosc sygnalu Stan. case Stan is -- Gdy obecny stan to S0 i przelacznik DIP nr 8 na plytce ElbertV2 jest w pozycji ON, -- to nastepny stan to S1; when S0 => if (not DPSwitch(0)) = '1' then Stan <= S1; else Stan <= S0; end if; -- Gdy obecny stan to S1 i przelacznik DIP nr 7 na plytce ElbertV2 jest w pozycji ON, -- to nastepny stan to S2; when S1 => if (not DPSwitch(1)) = '1' then Stan <= S2; else Stan <= S1; end if; -- Gdy obecny stan to S2 i przelacznik DIP nr 8 na plytce ElbertV2 jest w pozycji OFF, -- to nastepny stan to S3; when S2 => if (not DPSwitch(0)) = '0' then Stan <= S3; else Stan <= S2; end if; -- Gdy obecny stan to S3 i przelacznik DIP nr 7 na plytce ElbertV2 jest w pozycji OFF, -- to nastepny stan to S0; when S3 => if (not DPSwitch(1)) = '0' then Stan <= S0; else Stan <= S3; end if; -- Gdy wartosc sygnalu Stan obierze wartosc nieustalona to uklad przejdzie w stan S0; when others => Stan <= S0; end case; end if; end process; |

Jak widać (po komentarzach) blok process jest wykonywany przy każdej zmianie stanu sygnału zegarowego. Ponadto instrukcja warunkowa wyznacza, że wnętrze bloku process będzie wykonywane dla każdego narastającego zbocza sygnału zegarowego.

Dalej znajduje się blok case-when. Instrukcja ta sprawdza wartość sygnału znajdującego się za case i wykonuje blok instrukcji znajdujący się za odpowiednim when. Przykładowo, gdy wartość sygnału Stan wyniesie S3, to zostanie wykonany blok when S3.

Oczywiście jest to instrukcja analogiczna do instrukcji switch-case

znanej z innych języków programowania.

Zawartość bloku case opisuje właśnie zachowanie naszego układu (zgodnie z wcześniejszym diagramem). Przykładowo w sytuacji, gdy układ jest w stanie S0 i DIP8 będzie w pozycji ON (co jest opisane wyrażeniem: (not DPSwitch(0)) = '1')), to w chwili spełnienia tego warunku układ przejdzie w stan S1. W przeciwnym wypadku urządzenie pozostanie w stanie S0. Pozostałe stany są analogicznym odwzorowaniem diagramu.

Warto w tym miejscu jeszcze wspomnieć o tym, że dobrą praktyką jest stosowanie dodatkowego przypadku w bloku case. Mowa o bloku when others, bardzo często programy do syntezy (np. Xilinx ISE) mogą zgłaszać ostrzeżenia lub nawet błędy, gdy tego bloku zabraknie. Ma to na celu uniknięcie stworzenia "zatrzasków" (ang. latches) w układzie.

Temat zjawiska powstawania zatrzasków wykracza poza ramy tego kursu. Zagadnienie to jest związane ze sztuką projektowania układów cyfrowych i ma za zadanie takie konstruowanie układów, by wykluczyć niepożądane stany nieustalone.

Na końcu naszego kodu znajdują się instrukcje, które przypisują wyjścia układy na diody:

|

1 2 3 4 5 6 |

-- Ponizsze instrukcje przenosza wartosc stanu na diody LED -- np. jesli sygnal Stan jest rowny S0 to wlaczy sie dioda LED0 (D8 na plytce ElbertV2); LED(0) <= '1' WHEN Stan=S0 ELSE '0'; LED(1) <= '1' WHEN Stan=S1 ELSE '0'; LED(2) <= '1' WHEN Stan=S2 ELSE '0'; LED(3) <= '1' WHEN Stan=S3 ELSE '0'; |

Zgodnie z diagramem stanów zależnie od wartości sygnału Stan dana dioda jest włączana albo nie. Można tutaj zobaczyć nową konstrukcje WHEN-ELSE, która należy do zbioru instrukcji współbieżnych (wykonywanej w sposób natychmiastowy i ciągły). Jej działanie odpowiada pojedynczej instrukcji warunkowej. Gdy warunek umieszczony po WHEN jest spełniony to zostaje wykonane przypisanie wartości umieszczonej przed WHEN. W innych przypadkach następuje przypisanie wartości umieszczonej po ELSE.

Przykładowo, gdy sygnał Stan osiągnie wartość S0 to do LED(0) będzie przypisane logiczne 1. W innych przypadkach dioda będzie miała przypisaną wartość logiczną 0.

Poniżej, dla pewności, znajduje się cały program dla tego projektu:

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63 64 65 66 67 68 69 70 71 72 73 74 75 76 77 78 79 80 81 82 83 84 85 86 87 88 |

-- dodajemy biblioteki library IEEE; use IEEE.STD_LOGIC_1164.ALL; entity maszyna_stanow is Port ( Clk : in STD_LOGIC; -- sygnal zegarowy jest uzywany w bloku process odpowiadajacym za dzialanie naszej maszyny stanow DPSwitch : in STD_LOGIC_VECTOR(1 downto 0); -- dwa przelaczniki DIP z ktorych korzystamy do poruszania sie pomiedzy stanami LED : out STD_LOGIC_VECTOR(3 downto 0)); -- 4 diody LED jako wyjscia end maszyna_stanow; architecture Behavioral of maszyna_stanow is -- ponizsza instrukcja definiuje nowy rodzaj sygnalu, ktory moze przyjac jedynie te wartosci -- ktore sa wymienione w nawiasie - konstrukcja ta jest podobna do definicji enum znanej z jezyka programowania C type typ_stanu is (S0, S1, S2, S3); -- Definiowanie stanow signal Stan : typ_stanu := S0; -- Tworzenie sygnalu - zmiennej mogacej przyjmowac wartosci zdefiniowane w State_Type; begin process (Clk) begin if rising_edge(Clk) then -- gdy nastapi narastajace zbocze sygnalu zegarowego -- instrukcje zawarte ponizej beda wykonane -- Instrukcja CASE sprawdza wartosc sygnalu Stan, -- bazujac na jego wartosci jest wykonywany okreslony blok WHEN -- ktory jest wstanie zmienic wartosc sygnalu Stan. case Stan is -- Gdy obecny stan to S0 i przelacznik DIP nr 8 na plytce ElbertV2 jest w pozycji ON, -- to nastepny stan to S1; when S0 => if (not DPSwitch(0)) = '1' then Stan <= S1; else Stan <= S0; end if; -- Gdy obecny stan to S1 i przelacznik DIP nr 7 na plytce ElbertV2 jest w pozycji ON, -- to nastepny stan to S2; when S1 => if (not DPSwitch(1)) = '1' then Stan <= S2; else Stan <= S1; end if; -- Gdy obecny stan to S2 i przelacznik DIP nr 8 na plytce ElbertV2 jest w pozycji OFF, -- to nastepny stan to S3; when S2 => if (not DPSwitch(0)) = '0' then Stan <= S3; else Stan <= S2; end if; -- Gdy obecny stan to S3 i przelacznik DIP nr 7 na plytce ElbertV2 jest w pozycji OFF, -- to nastepny stan to S0; when S3 => if (not DPSwitch(1)) = '0' then Stan <= S0; else Stan <= S3; end if; -- Gdy wartosc sygnalu Stan obierze wartosc nieustalona to uklad przejdzie w stan S0; when others => Stan <= S0; end case; end if; end process; -- Ponizsze instrukcje przenosza wartosc stanu na diody LED -- np. jesli sygnal Stan jest rowny S0 to wlaczy sie dioda LED0 (D8 na plytce ElbertV2); LED(0) <= '1' WHEN Stan=S0 ELSE '0'; LED(1) <= '1' WHEN Stan=S1 ELSE '0'; LED(2) <= '1' WHEN Stan=S2 ELSE '0'; LED(3) <= '1' WHEN Stan=S3 ELSE '0'; end Behavioral; |

Dodanie pliku UCF

Podobnie jak w poprzednich projektach można napisać własny plik lub skorzystać z gotowego:

|

1 2 3 4 5 6 7 8 9 |

NET "Clk" LOC = P129 | IOSTANDARD = LVCMOS33 | PERIOD = 12MHz; NET "LED[0]" LOC = P46 | IOSTANDARD = LVCMOS33 | SLEW = SLOW | DRIVE = 12; NET "LED[1]" LOC = P47 | IOSTANDARD = LVCMOS33 | SLEW = SLOW | DRIVE = 12; NET "LED[2]" LOC = P48 | IOSTANDARD = LVCMOS33 | SLEW = SLOW | DRIVE = 12; NET "LED[3]" LOC = P49 | IOSTANDARD = LVCMOS33 | SLEW = SLOW | DRIVE = 12; NET "DPSwitch[0]" LOC = P70 | PULLUP | IOSTANDARD = LVCMOS33 | SLEW = SLOW | DRIVE = 12; NET "DPSwitch[1]" LOC = P69 | PULLUP | IOSTANDARD = LVCMOS33 | SLEW = SLOW | DRIVE = 12; |

Działanie układu w praktyce

Pora sprawdzić układ w praktyce. Przesuwamy przełącznik w pozycję OFF i uruchamiamy układ. Po jego włączeniu powinna świecić się jedna skrajna dioda. Czyli wszystko się zgadza z pierwszymi założeniami. Teraz można sprawdzić, czy cały układ działa poprawnie.

Pomocny będzie graf:

Analizujemy kolejne elementy:

- Przełączamy DIP7 na ON i wracamy na OFF (można kilka razy) - nic się nie dzieje. Przełączamy DIP8 na ON i układ przechodzi z S0 do S1.

- Przełączamy DIP8 na OFF i wracamy na ON - nic się nie dzieje. Przełączamy DIP7 na ON i układ przechodzi z S1 do S2.

- Przełączamy DIP7 na OFF i wracamy na ON - nic się nie dzieje. Przełączamy DIP8 na OFF i układ przechodzi z S2 do S3.

- Przełączamy DIP8 na OFF i wracamy na ON - nic się nie dzieje. Przełączamy DIP7 na OFF i układ przechodzi z S3 do S0.

- Procedura rozpoczyna się od początku.

Wszystko zgadza się idealnie z grafem!

Układ działa, ale ma pewne niedoskonałości, które widać gdy się pobawimy przyciskami trochę "losowo". Czasami nasz automat przeskakuje jeden stan lub się cofa! Czy to prawda? Zachęcam do zastanowienia się czym powodowane są dziwne zachowania i czy faktycznie jest to błąd, czy może wynika to z naszego prostego diagramu?

Podsumowanie

Celem artykułu było delikatne wprowadzenie automatów skończonych. Specjalnie nie poruszaliśmy tutaj praktycznie żadnej teorii, tylko szybko przeszliśmy do prostego przykładu, aby pokazać, że to nic strasznego. W praktyce rozwiązanie to przydaje się podczas pisania wielu programów (nie tylko na FPGA). Szczególnie, gdy działanie układu składa się z kilku wyraźnie odrębnych stanów, które muszą następować po sobie w odpowiedniej kolejności.

W kolejnej części kursu podstaw VHDL stworzymy układ, który również będzie miał tylko 4 stany, jednak pojawi się w nim znacznie więcej zawiłości. Konieczne będzie również poradzenie sobie z problemem drgań styków w przyciskach. W tym celu przygotujemy osobny moduł podrzędny.

Nawigacja kursu

Autor kursu: Adam Bemski

Redakcja: Damian Szymański

Ilustracje, testy: Piotr Adamczyk

Powiązane wpisy

automat, fpga, kursFPGA, maszyna, stan, vhdl

Trwa ładowanie komentarzy...